The German Fraunhofer Heinrich Hertz Institute HHI and Silicon Valley Missing Link Electronics (MLE) collaborate to optimize 25G/50G Ethernet Low-Latency Media Access Controller (MAC) for Xilinx Ultrascale+ Transceiver Technology.

“With Xilinx Ultrascale+ transceivers reaching up to 30.5 Gbps, 100 Gigabit Ethernet connectivity becomes a reality. This is reflected by the fact that Xilinx has integrated hard macros for 100GE MAC into their devices. However, many high-performance embedded, test & measurement or automotive applications are fully served by more cost-efficient 25G or 50G Ethernet. Our Low-Latency MAC soft IP Core addresses that gap”, says Dr. Johannes Fischer, Head of Fraunhofer HHI’s Digital Signal Processing Group.

“MLE has been collaborating with Fraunhofer HHI for several years on enabling high-speed connectivity solutions for Xilinx customers. Our team currently markets and supports Fraunhofer HHI’s proven 10GE MAC, and a corresponding TCP/IP stack, all made available through the Xilinx website. We are looking forward to offering 25G/50G Ethernet solutions to our customer base, soon”, underlines Dr. Endric Schubert, CTO at MLE.

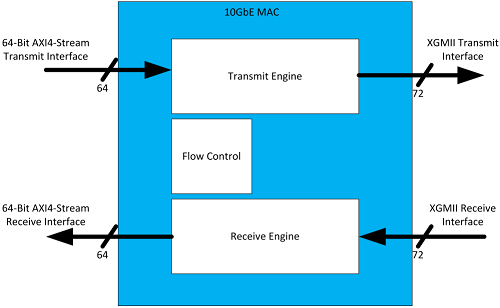

The 10GE MAC IP-Core from Fraunhofer HHI is a low latency Ethernet Media Access Controller (MAC) according to the IEEE802.3 -2008 specification. The IP Core was specifically designed to have the lowest possible latency, and to be as resource efficient as possible at the same time. The 10GE MAC IP-Core is listed at Xilinx library of Intellectual Property (IP) under https://www.xilinx.com/products/intellectual-property/1-o0w4k1.html.

The 25GE MAC IP-Core will be released early Q4 2017, and its’ 50GE MAC IP-Core counterpart later that year. Device Family Support will include Xilinx Virtex UltraScale+ Kintex UltraScale+ Zynq UltraScale+ MPSoC Virtex.

Advertisement

Learn more about Xilinx