SiFive has introduced the Freedom family of open-source SoC-platform intellectual property based on the RISC-V instruction set architecture. The company offers the Freedom U500 and Freedom E300 processing platforms that are a new approach to designing and producing SoCs in that they are based on open-source and extensible architecture with no licensing fees.

The platforms provide the ability to create silicon enhancements and customizations, which SiFive then incorporates and delivers to the customer at a lower cost and faster time-to-market than traditional custom silicon designs. The platforms are said to provide significant performance and power advantages over existing microcontrollers and FPGAs.

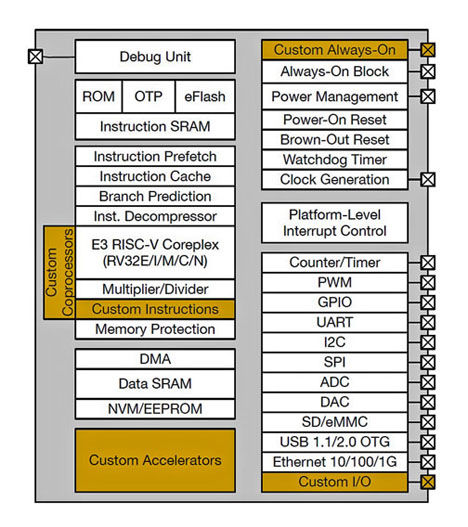

The E300 Everywhere version targets embedded processing, IoT, and wearables markets. Designed in TSMC 180 nm, it is the most efficient RISC-V core and includes support for RISC-V compressed instructions, which have been shown to reduce code size by up to 30%. It includes the E3 RISC-V Coreplex processor with single-issue in-order 32-bit execution pipeline, integrated instruction and data memories, a platform-level interrupt controller, and an on-chip debug unit. The E3 Coreplex can optionally implement pre-fetch buffers and/or an instruction cache. The platform can be adapted with customer-specific instruction-set extensions, custom co-processors, custom accelerators, custom I/O, and always-on blocks.

Fig. 1: The E300 customizable RISC-V SoC IP block diagram.

The on-chip memory system can be flexibly configured to include ROM, OTP, eFLASH, NVM/EEPROM, and/or SRAM of various sizes. The IPs interrupt controller supports programmable priority levels, and, with the addition of the N extension, supports nested interrupt handling for fast response. The available RISC-V ISA standard C extension reduces code size and dynamic energy consumption while increasing performance by adding additional 16-bit compressed instruction encodings.

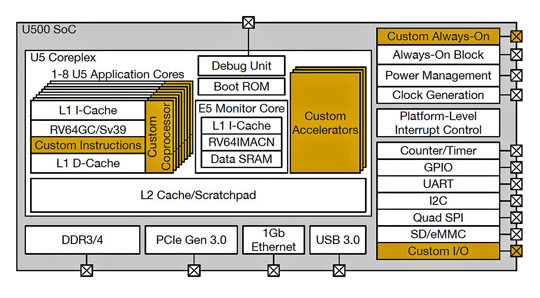

The U500 Unleashed version customizable RISC-V SoC IP contains the configurable high-performance U5-Coreplex 1.6 GHz+ cache-coherent 64-bit multiprocessor with up to eight cores and application-specific custom hardware. The fully Linux-capable IP can reduce NRE and time-to-market for customized SoC designs in markets such as machine learning, storage, and networking. Available high-speed peripherals include PCIe 3.0, USB3.0, GbE, and DDR3/4. The design is compatible with a TSMC 28-nm process.

Fig. 2: The U500 customizable RISC-V SoC IP block diagram.

SiFive's hardware designs leverage the body of software and tools available from the open-source community under the guidance of the RISC-V Foundation, which supports the basic processor architecture. This is said to dramatically reduce the cost of developing custom silicon. The company says Freedom SoCs can be designed and built to final complete prototype for as little as upper six-figure to lower seven-figure total cost.

FPGA development boards with pre-configured designs are available to support development of software and hardware for both versions. Developers can find out more and register at dev.sifive.com.

Advertisement

Learn more about SiFive