Microsemi Corporation, a leading provider of semiconductor solutions differentiated by power, security, reliability and performance, announced the release of its SoftConsole version 5.1, the world’s first available Windows-hosted Eclipse integrated development environment (IDE) for designs utilizing RISC-V open instruction set architectures (ISAs) such as RV32I. SoftConsole, Microsemi’s free software development environment enabling rapid production of C and C++ programming language designs for its field programmable gate arrays (FPGAs), will be showcased at the Design Automation Conference (DAC) in a presentation highlighting its open architecture, low power and development capabilities using RISC-V soft central processing unit (CPU) cores.

“With the majority of Microsemi FPGA designers utilizing a Windows platform for their development efforts, SoftConsole v5.1 not only supports our RISC-V soft CPU cores to enable designs with our highly secure and reliable FPGAs, but it can also be used for any RV32I standard ISA extensions,” said Tim Morin, director of marketing at Microsemi. “This product release broadens the RISC-V ecosystem for those developing on Windows machines, and leverages our leadership position as we continue investing in this architecture to provide customers dependable, long-term roadmap support.”

Microsemi’s SoftConsole v5.1, a GNU compiler collection (GCC), now supports both Windows and Linux for RISC-V designs and can be used for RV32I implementations including extensions to the baseline RV32I architecture such as M,A,F,D,G and C. Offering low power and an open architecture, it supports Microsemi’s PolarFire™, RTG4™, SmartFusion™2 and IGLOO™2 FPGA-based RISC-V soft CPUs as well as the HiFive1 Arduino kit from SiFive, a fabless semiconductor company that produces computer chips based on the RISC-V ISA. SoftConsole v5.1 is ideal for developing a wide variety of applications within the aerospace and defense, communications, data center and industrial markets.

RISC-V, an ISA which is now a standard open architecture under the governance of the RISC-V Foundation, offers numerous benefits, including enabling the open source community to test and improve cores at a faster pace than closed ISAs. As the RISC-V intellectual property (IP) core is not encrypted, it can be used to ensure trust and certifications not possible with closed architectures. Portability is another benefit of the technology. For example, designers can begin development with Microsemi’s RISC-V core in its FPGAs and then move to an application-specific integrated circuit (ASIC) royalty-free.

“Rumble Development is excited Microsemi is investing in RISC-V with its IP core and the new version of the SoftConsole IDE,” said Michael Aronson, president of Rumble Development, a customer of Microsemi which provides custom logic solutions to original equipment manufacturers (OEMs). “We believe the portability, stability and openness of this ISA combined with Microsemi’s ecosystem will enable us to innovate faster and deliver best-in-class solutions.”

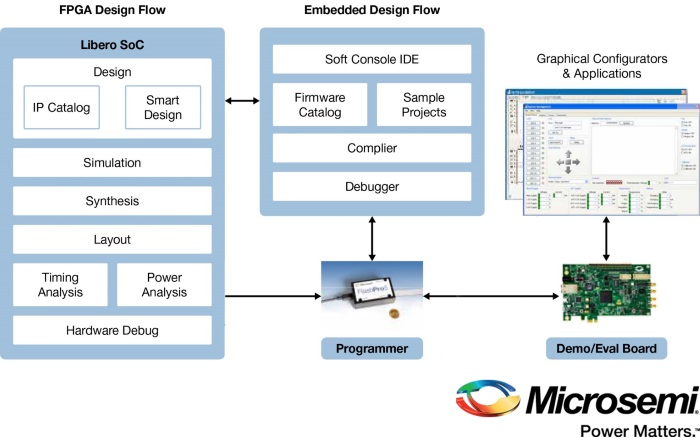

As a free software development environment supporting quick development of C and C++ executables for Microsemi’s FPGAs using RISC-V soft CPU cores, SoftConsole v5.1 provides a flexible and easy-to-use graphical interface for managing embedded software development projects. Customers can quickly develop and debug software programs and implement them in Microsemi FPGAs, with a fully integrated debugger offering easy access to memory contents, registers and single-step execution. SoftConsole also enables users to configure project settings and organize files, provides simultaneous access to multiple tool windows, and delivers the ability to quickly switch editing and debug views. In addition, Libero SoC, Microsemi’s comprehensive suite of FPGA design tools, includes the Firmware Catalog to export firmware for soft CPU FPGA designs which can be imported into SoftConsole.

The RISC-V ISA was named Best Technology of 2016 by The Linley Group at its annual Analysts’ Choice Awards in January 2017, where its principal analyst Linley Gwennap expressed support of the emerging technology.

“RISC-V is a modern take on the classic RISC instruction set, providing a clean and extensible approach suitable for a broad range of microprocessor implementations. More significantly, the open source, royalty-free RISC-V instruction set creates a new business model for CPU designers,” said Gwennap. “This combination has generated sizable industry interest in RISC-V, which will lead to several commercial deployments this year and beyond.”

Through Microsemi’s early involvement in the creation of the RISC-V Foundation, the company has an established leadership role in the emerging standard and ecosystem and is working closely with the nonprofit to ensure the ISA becomes an industry standard for a wide variety of computing devices. Ted Speers, head of product architecture and planning for Microsemi’s SoC business unit, was appointed to the inaugural board of directors of the RISC-V Foundation in July 2016, and Ted Marena, director of SoC FPGA marketing, was elected as vice-chair of the RISC-V Marketing Committee in August 2016.

Advertisement

Learn more about Microsemi