This reference design demonstrates how to achieve multiple ADC interleaving with high sampling rates and good resolution at low BOM-cost. The reference design was built with electronic imaging systems in mind. High definition imaging and other high speed signal processing applications require ADCs that can achieve high resolution, high SNR, high speed and low power consumption. These requirements cannot always be met with a single chip. By interleaving multiple SAR ADCs, the design optimizes trade-offs between different ADCs in order to meet all of the system requirements.

Features:

- Resolution: 14-bit

- input type: unipolar single-ended

- SNR > 73dB, ENOB: 12-bit, THD

- Power:

- Low latency compared to pipeline ADC-based solution

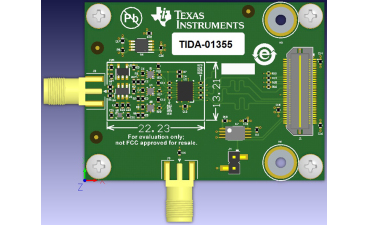

- Small form factor: 22mm x 13mm

Parts Include:

ADS7056 14-Bit 2.5MSPS Ultra-Low-Power Ultra-Small-Size SAR ADC With SPI Interface

LP5907 250mA Ultralow-Noise Low-IQ LDO

OPA836 Very Low Power, Rail to Rail out, Negative Rail in, VFB Op Amp

REF2033 Low-Drift, Low-Power, Dual-Output VREF and VREF/2 Voltage Reference

SN74AUCH244 Octal Buffer/Driver with 3-State Outputs

Learn more by downloading the reference design below

Advertisement

Learn more about Texas Instruments