By Jean-Jacques DeLisle, contributing writer

For a processor provider, the promise of a 15 to 20 times reduction in power without sacrificing peak performance and requiring extensive redesign may, at first, seem too much to ask. With billions of new CPUs, Internet of Things (IoT), and embedded processors likely to be sold in the upcoming years, harnessing any competitive edge and enabling new applications could be an extremely profitable venture. Minima Processor and ARM seem to agree that power consumption is one of the most limiting factors of a processors operation and that finding a solution to reduce power is a holy grail to a wealth of new opportunities.

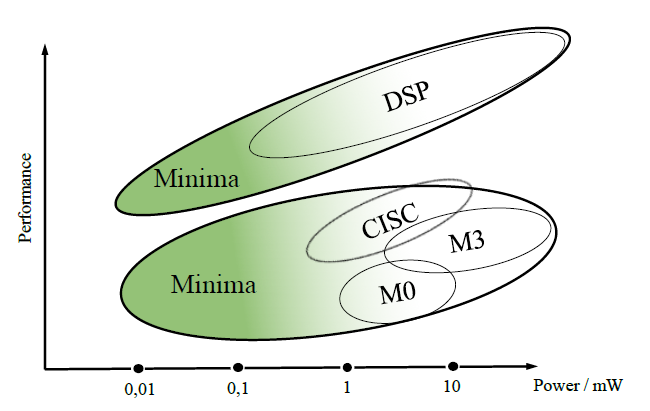

In order to realize this potential, Minima Processors has developed IP, which enables a regular CPU or DSP to leverage a dynamic margining and reduce power consumption. This method allows for a device to operate at a much lower power for any task, data, and under any condition. Minima’s dynamic margining approach also includes an ultra-wide dynamic voltage and frequency (DVFS) implementation with more significant energy reductions than standard DVFS approaches.

Image source: Minima Processor.

With enhanced low-power design, IoT devices would benefit from extended battery life, more powerful processors could be used in power-limited systems, and more cost-effective and compact thermal management solutions could be used. Though known since the 1970s, new investigation of near-threshold design techniques could bring about these energy savings.

Prior attempts at near-threshold design were rendered undesirable, as accounting for process variation and environmental factors on transistor behavior required operation parameters that reached a point of diminishing returns of energy savings. Moreover, transistor models and characterization methods focused on common modes of operation, and design techniques for near-threshold design could benefit from many existing simulation and design tools.

Minima’s technology bypasses the static approach to margining based on worst-case intersections of power and performance, which limits a processor’s performance for all conditions. This new approach leverages dynamic margining, which adjusts the power and performance, in real time, according to the task and conditions at hand. In order to implement Minima’s technology, the IP involves taking existing processor and DSP architecture and adding hardware and software that better controls the device’s operating power. Using timing monitors along paths to detect power and performance behavior, this solution’s software then optimizes the device performance in response to these new conditions.

Seeing the potential of such an approach, ARM and Minima have partnered to produce an Arm Cortex-M3 processor using Minima’s dynamic margining technology with the no-license-fee model through Arm DesignStart. The Minima IP-enhanced ARM Cortex-M3 processor takes advantage of many of the Cortex-M3’s duty-cycled, low-power design features and variety of sleep mode options to create an extremely low-power end solution.

With physical and cost limitations preventing the use of the smallest transistor nodes possible from being applicable to a wide range of low-cost, low-power applications, techniques such as Minima’s dynamic margining are a natural solution to reduce power consumption without having to resort to entirely new transistor processes.

Advertisement

Learn more about Electronic Products Magazine