By Alex Pluemer, contributing writer

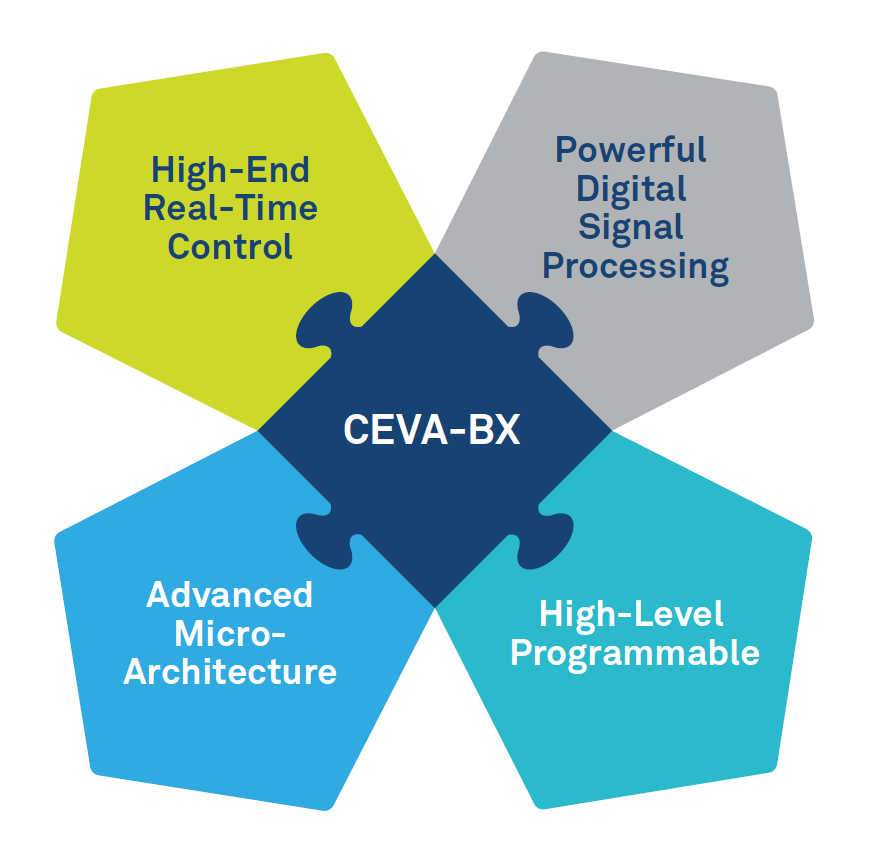

CEVA’s new CEVA-BX all-purpose, hybrid DSP/controller architecture integrates the high-level programming and compact code size required by large control code bases with the inherent low-power requirements of standard digital signal processor (DSP) kernels. The new architecture is designed for the next generation of algorithms used in digital signal processing for voice, video, sensing, communication, and digital signal control applications, extending CEVA’s reach into the automotive and industrial markets.

The CEVA-BX implements several integral principles of advanced microprocessor architectures, including native support for all standard C types, as well as a hardware loop buffer to reduce power consumption of code loops, a fully cached memory subsystem, a branch target buffer for minimizing branch overhead, and a large orthogonal general-purpose register set for maximizing C compiler efficiency.

The architecture also boasts superior control capabilities, as evidenced by its 4.5 CoreMark/MHz score. Users can incorporate proprietary instruction set architecture (ISA) using the CEVA-Xtend to leverage the company’s automatic queue and buffer management mechanisms to integrate co-processors and build a cluster of CEVA-BX cores.

In addition, CEVA-BX features an 11-stage pipeline and five-way VLIW micro-architecture to provide parallel processing with dual scalar compute engines, load/store, and program control and can achieve speeds of up to 2 GHz using the TSMC 7-nm process node and common standard cells and memory compilers. The CEVA-BX ISA provides support for single instruction, multiple data (SIMD) employed in neural-network inference, noise reduction, and echo cancellation. It also supports half-, single-, and double-precision floating-point units for high-accuracy sensor fusion and positioning algorithms.

CEVA-BX comes in two configurations:

- The CEVA-BX1 features a single 32 × 32-bit MAC and quad 16 × 16-bit MACs and provides up to 8 GMACS per second in support of low- to mid-range DSP workloads including protocol stacks, always-on sensor fusion, and cellular IoT applications.

- The CEVA-BX2 employs quad 32 × 32-bit MACs and octal 16 × 16-bit MACs that can support 16 × 8-bit and 8 × 8-bit MAC operations. Providing up to 16 GMACs per second, the CEVA-BX2 meets the demanding workloads of applications such as multi-microphone beamforming, neural networking for speech recognition, and 5G PHY control.

Dedicated trusted execution modes ensure compliance with the industry’s safety and security standards. Both configurations are supported by a software development tool chain that includes an advanced LLM compiler, an Eclipse-based debugger, DSP and neural-network compute libraries, and neural-network framework support including Android NN API, AMR NN, and TensorFlow Lite. Users also can choose from among a variety of real-time operating systems.

CEVA-BX cores will be available for general licensing by the end of Q1 2019.

Advertisement

Learn more about Electronic Products Magazine