Taking gallium nitride power ICs to the next level, researchers at Imec report co-integration of Schottky barrier diodes and high-electron-mobility transistors (HEMTs) on a smart power platform.

The advance, reported during this week’s International Electron Devices Meeting, combines high-performance Schottky barrier diodes and depletion-mode HEMTs on a p-channel GaN, HEMT-based, 200-V, silicon-on-insulator power IC. The platform was developed on a 200-mm substrate, the researchers said.

The combination enables chip designs with increased functionality and performance. Imec said the integration paves the way for smaller, more efficient DC/DC and point-of-load converters.

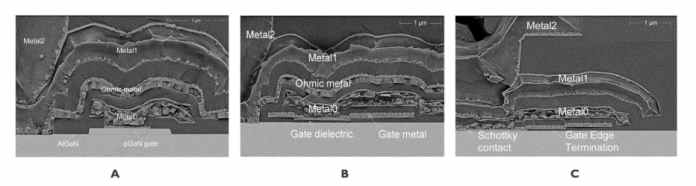

Process cross-sections of the high-voltage components fabricated on 200 mm GaN-on SOI substrates (a) e-mode pGaN-HEMT (b) d-mode MIS-HEMT, (c) Schottky barrier diode. All devices include metal field plates based on front-end and interconnect metal layers and separated by dielectric layers. Click for a larger image.(Source: Imec)

“The d-mode HEMT allows improvement of the logic [and] analog functions by replacing the inverting functions from RTL [Resistor/Transistor Logic] by DCFL [Direct-Coupled FET Logic], which improves the pull-up characteristics of the inverting gates,” Stefaan Decoutere, Imec’s program director for GaN technology, noted in an interview.

“There are no good p-channel devices in GaN–the mobility is about 60 times lower of holes compared to electrons–such that complementary logic like in CMOS is not realistic. The low-voltage Schottky diode offers additional functionality on-chip, such as level shifting and clamping. The high-voltage power Schottky diode can be used to improve the third quadrant operation of the low-side switch” for better power efficiency, Decoutere added.

The next step is developing a GaN IC prototype and a process transfer to a less expensive 200-mm substrate. Previously, “GaN-on-Si was processed on smaller diameter wafers [4 and 6 inch], and more fabs have moved their GaN technology to 200 millimeter,” Decoutere said.

The challenge for larger diameter GaN-on-Si substrates is the mechanical stability of substrates, given the mismatch between the coefficient of thermal expansion of the GaN/AlGaN layers and the underlying substrate. “With proper design of the buffer, [such as] the use of superlattice buffers, and improved MOCVD deposition tools, this mechanical stability issue has been addressed, making it feasible to process GaN on 200-mm substrates,” the Imec researcher said.

Read the complete article at sister publication EE Times.

Advertisement