Researchers from The Grainger College of Engineering at the University of Illinois Urbana-Champaign (UIUC), in collaboration with PragmatIC Semiconductor, a flexible electronics manufacturer, have claimed the first commercially viable flexible plastic microprocessors. For less than a penny each, these FlexiCore chips can make low-cost smart consumer products. In addition, the flexible technology enables the chips to meet size constraints in these applications.

“You could put processors on bandages to detect whether a wound is healing or add them to consumer goods packaging to track progress along the supply chain,” said Rakesh Kumar, a professor of electrical and computer engineering and researcher in the Coordinated Science Lab at UIUC, in a statement. “The challenge has been creating a processor that can be both cheaply produced and flexible enough to fit snugly even against uneven surfaces on our body, packages, or beer bottles.”

Instead of using silicon, the researchers decided to use plastic as the foundation of its chips. The FlexiCores are built on thin-film transistors (TFTs) made with indium-gallium-zinc oxide (IGZO), a semiconductor material that works even when bent and is compatible with plastic.

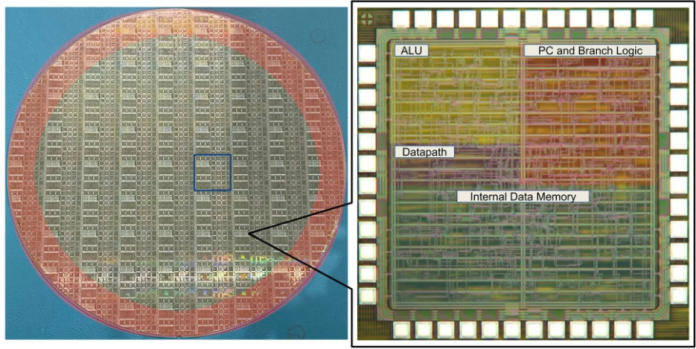

FlexiCore4 dies on 200-mm wafer. Click for a larger image. (Source: University of Illinois Urbana-Champaign)

Polyimide has proven to be a resilient, flexible substrate, said Nathaniel Bleier, graduate electrical and computer engineering and lead student on the project. “The TFTs are inorganic — made of indium, gallium, zinc, and oxygen — and are deposited onto the polyimide substrate containing four metal layers. The process is a photolithographic process that uses sequences of deposition, patterning, and etching steps.”

The UIUC team tested 4-bit and 8-bit processors and found that the 4-bit processors produced a yield of 81%, which is high enough for the chips to be manufactured for less than a penny each. The 4-bit processor has 2,104 devices (transistors and resistors), which is much less than the 56,000-plus devices on a plastic Arm processor, called PlasticArm, announced last year.

The researchers tested the cores at 12.5 kHz at 3 V and 4.5 V. The cores consumed 3.9/4.9 mW on average. The FlexiCore4 and FlexiCore8 cores measure 5.56 mm2 and 6.05 mm2, respectively. Both were tested on wafer and unpackaged.

Bleier said testing the cores at 12.5 kHz was a limitation of the testing apparatus.

“We believe we can run the cores significantly faster and that increasing clock speed has minimal effect on power consumption, which is overwhelmingly static power,” he said.

Why select 4-bit and 8-bit processors? “Our goal with this work was to show that flexible electronics enable low-cost microprocessors, which, in turn, allow computing to penetrate domains that, to the present, have not seen a proliferation of computing due to conformality, thinness, and cost requirements. These domains include packaging for fast-moving consumer goods; low-end health-care products such as adhesive bandages; disposable food sensors; and sensors for the forest, agriculture, and environmental monitoring.

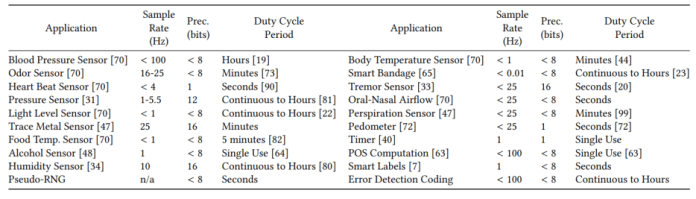

“A low-cost, flexible processor that can meet these domain requirements requires a low-area, high-yield microprocessor,” Bleier added. “Further, analysis of the domain applications [see table below] shows that most of these ‘flexible applications’ require no more than 8-bit data precision, and in fact, 4 bits is even overkill for many.”

Example applications and their performance requirements for the FlexiCore flexible plastic microprocessors. Click for a larger image. (Source: University of Illinois Urbana-Champaign)

But there were big challenges. Designing a processor that is both sufficiently small and powerful “to be useful for real computational work has been the the biggest challenge in developing low-cost, flexible processors,” Bleier said.

The unit cost of a processor scales superlinearly with the processor’s size, and the material cost is directly proportional to processor size, he added. “So larger processors cost more per built processor and require building more processors to meet a production target. This means that to get ultra-low pricing, we need a very small processor, but the processor still needs to be able to support the flexible applications that require computation.”

Other prototypes

There are a few competitive flexible plastic microprocessors that have been announced over the past year, including Arm’s PlasticArm and imec’s 8-bit 6052 plastic processors. But there are several key differences among the prototypes. (See the UIUC/PragmatIC Semiconductor report for additional comparisons.)

Bleier said UIUC’s project differs from Arm’s work in several fundamental ways: “First, ours is truly a microprocessor capable of executing arbitrary programs written in its ISA. We leveraged this fact in our post-silicon testing and validation, where we rigorously tested each chip with >100,000 instructions from directed and randomized tests that exercise every single chip path. So when we say that a core works, we’re confident that it does indeed work.

“On the other hand, the Arm prototype executes a single program; thus, testing consists of checking to see if it correctly executed that program,” he added.

In terms of the imec prototype, it is more like the FlexiCore “in that they designed a processor that can execute arbitrary programs,” said Bleier.

However, both the imec and Arm projects adapted existing architectures designed for silicon, which UIUC’s researchers “think is a mistake.”

Bleier explained: “The original MOS 6502 was built on an 8-µm technology [process] node — i.e., 10× bigger than used in these flexible works — but could still operate in the low-megahertz frequency range. Further, MOS 6502 can address 64 KB of memory — ARMv6m can address 4 GB of memory. Despite this, Arm includes only about 128 B of memory in its SoC. In flexible electronics, there is currently no need to be able to address huge (or even paltry) amounts of memory, since only tiny amounts of flexible memory can be built at this time.”

Another concern of the researchers is the microarchitectures to support the designs. They questioned their multi-cycle design approach, particularly for battery- or harvester-powered systems.

“While all commercial ARMv6m cores are pipelined, the PlasticArm, like the 6502, uses a multi-cycle design to minimize area — multi-cycle design allows temporal multiplexing of structures,” said Bleier. “What this means is that each instruction takes multiple cycles to execute. This is an acceptable tradeoff in technologies, like legacy silicon technologies, which are dominated by dynamic power. But this flexible technology is dominated by static power, meaning increasing the number of cycles per instruction corresponds to doubling, tripling, quadrupling, etc., the energy needed to execute an instruction.”

The UIUC team still has work ahead with three key goals: The researchers want to enable full systems that deliver confidential and authenticated communications to/from flexible applications, said Bleier. They also want to develop circuit and micro-architectural power reduction solutions and explore intermittent computing (i.e., computing in the presence of power failures) in the context of flexible electronics.

The team’s research for the FlexiCore flexible plastic microprocessors was presented at the International Symposium on Computer Architecture in June.

Advertisement