Artificial intelligence (AI) domain controllers address the need to deal with the large volume of data from a variety of sensors and high-speed processing and security, adding a wealth of features and capabilities previously unavailable. Ambarella has expanded its CV3 family, introducing the CV3-AD685 automotive AI domain controller, the first production version of the family.

The CV3-AD685’s CVflow AI neural vector processor (NVP) engine provides high performance, low latency, and low-power neural network (NN) processing. Fabricated using Samsung’s advanced 5-nm automotive process technology, target applications for the CV3-AD685 system-on-chip (SoC) include automated driving from L2+ to L4, single/multi-camara advanced driver assistance systems (ADAS), parking assistance systems, driver monitoring systems (DMS) and in cabin solutions and single/multi-channel electronic mirrors with blind spot detection (BSD).

The CV3-AD685 also delivers new radar processing capabilities and enables single-chip centralized processing of raw video and 4D imaging radar data in automotive applications.

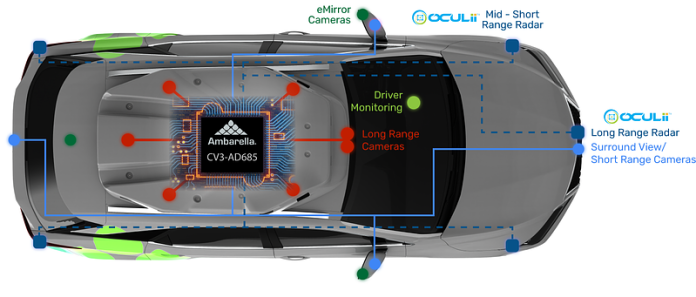

The CV3-AD685 provides a single-chip solution for multi-sensor perception, fusion and path planning (Source: Ambarella)

Ambarella claims that an on-chip image signal processor (ISP) provides outstanding imaging in low-light conditions, high dynamic range (HDR) processing for maximum image detail in high-contrast scenes, enhanced AI and computer vision capabilities, and clear video for viewing. It also delivers high-resolution video recording and streaming at very low bit rates with efficient encoding in H.265 and H.264 video formats.

The CVflow AI engine’s NN processing is 20× faster than the previous CV2 SoCs and offers additional general vector processing capabilities, providing overall performance for full autonomous driving (AD) stack processing including traditional computer vision processing plus optimization enhancements for HD radar, deep fusion and planning. It integrates advanced image processing, a dense stereo and optical flow engine, Arm Cortex A78AE and R52 CPUs, an automotive GPU for visualizations, and a hardware security module (HSM). The “algorithm first” architecture supports the entire AD software stack.

The HSM isolates different domains and secure software provisioning. Cybersecurity features include asymmetric/symmetric crypto acceleration, secure storage and key provisioning, encrypted CVflow tasks, true random number generator (TRNG), one-time programmable (OTP) memory, DRAM scrambling and DRAM virtualization.

Ambarella’s CVflow chip architecture is based on a deep understanding of core computer vision algorithms and includes a dedicated vision processing engine programmed with a high-level algorithm description. This allows the architecture to scale performance to trillions of operations per second using very little power. CVflow allows customers to map their own CNN networks trained with industry-standard tools (e.g., Caffe, TensorFlow, PyTorch) to run on Ambarella processors.

Ambarella announced the chip at the Consumer Electronics Show (CES). The company demonstrated the latest generation of its R&D vehicles running on the CV3 central domain controllers.

Advertisement

Learn more about Ambarella