A high level of deterministic fast response is required for functional safety needed in many of the latest automotive, industrial, aerospace, and medical designs, where there is a definite push for more autonomy in electronic systems. The new ARM Cortex-R52 core supports an adaptable memory architecture with deterministic tightly coupled memories integrated within the processor. Along with a low-latency peripheral port, this enables assured response latencies. The core meets the highest functional safety standards and is said to provide the robust, real-time performance needed for next-generation autonomous systems.

The ARM Cortex-R52 processor IP was designed from the ground up to address functional safety in systems that must comply with ISO 26262 ASIL D and IEC 61508 SIL 3 — the most stringent safety standards in the automotive and industrial markets. The IP offers hardware-enforced separation of software tasks to ensure that safety-critical code is fully isolated. This allows the hardware to be managed by a software hypervisor policing the execution and resourcing of tasks. By enabling the precise and robust separation of software, the Cortex-R52 decreases the amount of code that must be safety-certified, thus speeding up software integration, maintenance, and validation. The processor also deals with the increased software complexity involved with determinism and fast context switching that real-time systems demand.

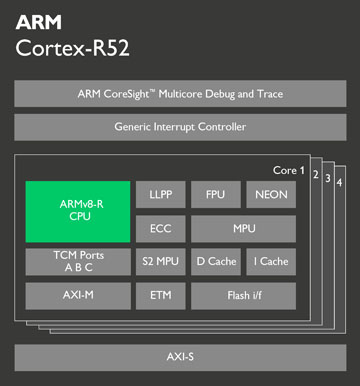

The processor IP has an eight-stage pipeline with instruction pre-fetch, branch prediction, superscalar in order execution, and parallel execution paths for load-store, MAC, shift-ALU, divide, and floating-point. It also features up to quad-core multi-processor configurations or eight logical cores in dual-core lock step (DCLS) configuration.

The core has a licensable extended safety package that is externally certified and high fault coverage core self-test library for boot time and periodic run-time execution. It supports up to three optional tightly coupled memory interfaces, each up to 1 Mbyte. The processor includes low-latency interrupt technology that allows long multi-cycle instructions to be interrupted and restarted. Deferral of lengthy memory accesses occurs in certain circumstances. It is configurable to support from 32 to 960 interrupts, including software-generated interrupts which can be routed between multiple cores.

There is support for level 1 and 2 memory protection units and single-bit error correction and double-bit error detection for cache and TCM memories. There is also a 128-bit AMBA AXI-4 bus master for Level-2 memory and peripheral access, with ECC protection. Two floating-point units can be implemented. A per-core dedicated 128-bit AMBA AXI port can integrate latency-sensitive flash memory tightly to a specific core, with configurable ECC protection. The Cortex-R52 includes a CoreSight Embedded Trace Module that can be configured per core or shared between the cores in the cluster.

Advertisement

Learn more about ARM