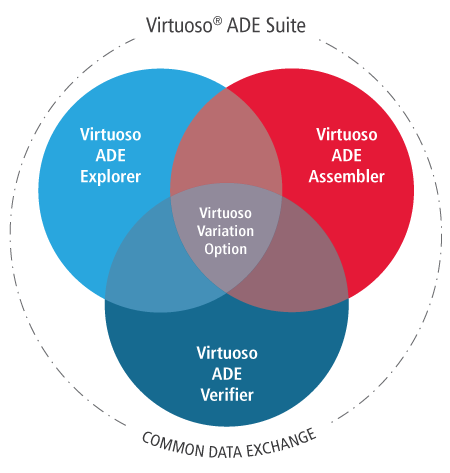

Cadence’s Virtuoso Analog Design Environment (ADE) suite offers up a rich set of tools to analog, mixed-signal, and RF IC designers. ADE’s Explorer component enables schematic probe placement, marching waveforms (waveform plots during the simulation instead of waiting until the end) so you don’t have to wait for a full simulation cycle if something is not working, pass/fail reports, and PVT corners plus Monte Carlo stats.

ADE’s Explorer component enables schematic probe placement, marching waveforms (waveform plots during the simulation instead of waiting until the end) so you don’t have to wait for a full simulation cycle if something is not working, pass/fail reports, and PVT corners plus Monte Carlo stats.

The Assembler analyzes your circuits with multi-stimulus test benches across corners and variations and compares circuit performance to design specifications. Separate “mini runs” perform conditional or dependent simulations. Existing-design migration to new technology nodes is supported.

ADE’s Verifier module links multiple tests across the design team, allowing you to easily verify that all of the moving pieces of the analog design are contributing to the overall design specifications set by your chip architect. Manual attempts to do this work often lead to mistakes because there is a disconnect between those methods and the design software.

Finally, the Variation option targets advanced node (≤16 nm) stats, yield estimation based on 5- and 6-sigma boundaries, easy creation of 3-sigma corners, and more.

Advertisement

Learn more about Cadence Design Systems