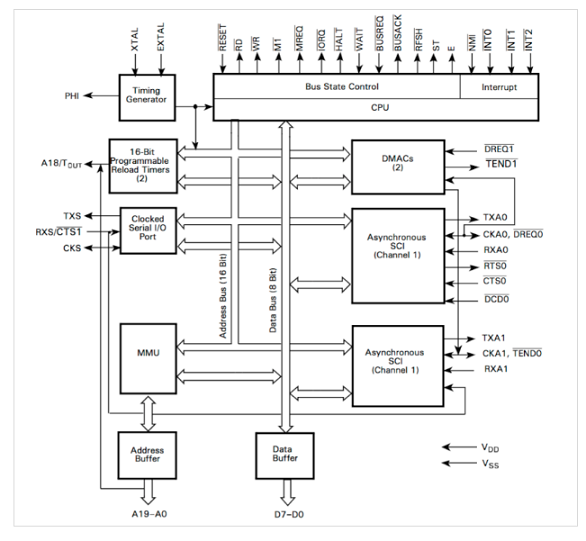

The enhanced Z8S180/Z8L180™ significantly improves on previous Z80180 models, while still providing full backward compatibility with existing ZiLOG Z80 devices. The Z8S180/Z8L180 now offers faster execution speeds, power-saving modes, and EMI noise reduction.

This enhanced Z180™ design also incorporates additional feature enhancements to the ASCIs, DMAs, and STANDBY mode power consumption. With the addition of ESCC-like Baud Rate Generators (BRGs), the two ASCIs offer the flexibility and capability to transfer data asynchronously at rates of up to 512 Kbps. In addition, the ASCI receiver features a 4-byte first in/first out (FIFO) buffer which reduces the likelihood of overrun errors. The DMAs have been modified to allow for chain-linking of the two DMA channels when set to take their DMA requests from the same peripherals device. This feature allows for nonstop DMA operation between the two DMA channels.

Not only does the Z8S180/Z8L180 consume less power during normal operations than the previous model, it offers three modes intended to further reduce power consumption. Power consumption during STANDBY Mode is reduced to 10 µA by stopping the external oscillators and internal clock. The SLEEP mode reduces power by placing the CPU into a stopped state, consuming less current while the on-chip I/O devices still operate. The SYSTEM STOP mode places both the CPU and the on-chip peripherals into a stopped mode, reducing power consumption even further.

Advertisement

Learn more about Zilog