Employing equalization techniques is an effective way of compensating for channel loss in JESD204B high speed serial interfaces for data converters. This reference design features the ADC16DX370, a dual 16-bit, 370 MSPS analog-to-digital converter (ADC) that utilizes de-emphasis equalization to prepare the 7.4 Gbps serial data for transmission. Configuration allows a user to optimize the de-emphasis setting (DEM) and output voltage swing setting (VOD) of the output driver to inversely match the characteristics of the channel. Experiments demonstrate the reception of a clean data eye over 20” of FR-4 material at the full data rate.

Features

• Achieve a high performance JESD204B serial link using low cost PCB materials

• Understand the limitations of lossy channels and equalization techniques to overcome the limitations

• Use a formula-based approach to optimizing the equalization features of the ADC16DX370

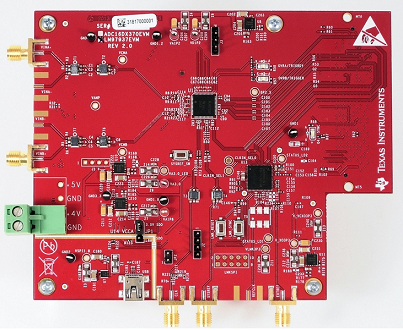

• This reference design is tested and includes an EVM, configuration software and User's Guide

Parts Include:

ADC16DX370 Dual 16-bit 370 MSPS ADC, 7.4 Gbps JESD204B Outputs

LM97937 Dual Channel 370MSPS Receiver and Feedback IC

LMH6521 High Performance Dual DVGA

LMK04828 Ultra Low Jitter Synthesizer and Jitter Cleaner

LP3878-ADJ Micropower 800mA Low Noise 'Ceramic Stable' Adjustable Voltage Regulator for 1V to 5V App.

SN74AVC4T774 4-Bit Dual-Supply Bus Transceiver With Configurable Voltage Translation and 3-State Outputs

Learn more by downloading the reference design below

Advertisement

Learn more about Texas Instruments