By Martin Rowe, senior technical editor, test & measurement, EDN & EE Times

You’ve probably heard the phrase “It takes a village to raise a child.” The same can be said for high-speed digital design. That’s the lesson that engineers at eSilicon, Wild River Technologies, and Samtec learned when eSilicon needed a board to test its latest 56-/112-Gbits/s PAM4 SerDes for use in IEEE 802.3bs (200-/400-Gbits/s Ethernet) and several Optical Internetworking Forum (OIF) implementations.

To find out how the three companies worked on the problem, I met on Jan. 30 with representatives of the three companies at DesignCon 2019 in Santa Clara, California.

“We needed a way to evaluate our chip,” said eSilicon’s director of field applications, Tim Horel. The board (Fig. 1 ) not only lets eSilicon engineers do that, it also serves as a reference design. The goal was to design a board that could pass data at a bit-error ratio (BER ) of 10E-11 over 5 m of copper cable without the need for forward-error correction (FEC ). The board, which was on display at DesignCon 2019, can maintain that BER over 7 m of copper, according to eSilicon’s director of marketing, Mike Gianfanga.

![]()

Fig. 1: A test board for eSilicon’s 56-/112-Gbits/s SerDes is based on Samtec’s Bulls Eye connectors that provide direct contact to the board. The board was on display at DesignCon 2019. Image: Martin Rowe.

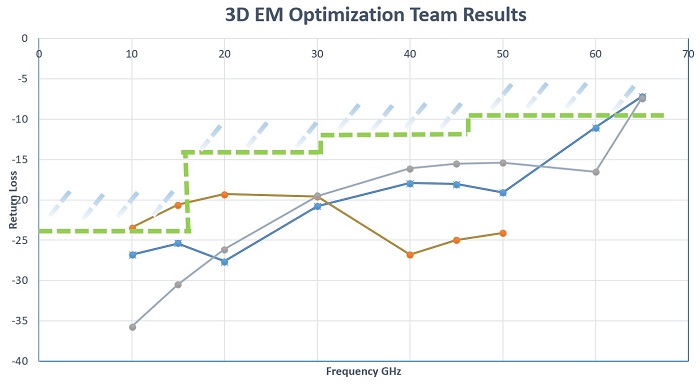

Rather than rely on a single approach to board design, Wild River Technology’s CTO, Al Neves, assembled three independent teams, one at Samtec and two at Wild River. Each used different design and simulation tools with the two Wild River teams using ANSYS HFSS and Simbeor THz software. Fig. 2 shows the results of return loss measurements for each design team. The green dashed line represents performance limits based on IEEE P370 .

“We needed agreement from the teams to know if we had the right design,” said Neves. “Along the way, we broke EDA tools every week.”

Fig. 2: Return loss measurements from three teams needed agreement for the design to continue. Image: Wild River Technology.

The board uses Samtec’s Bulls Eye connectors to pass the high-speed signals. These connectors require no soldering; solder results in unacceptable return loss. Instead, connections are made with pins to the board that each make three points of contact. A compression fit holds the connector in place.

“We bent the cables to make sure the pins kept in contact with the board,” said Neves. “The connections didn’t break.”

The engineers modeled the high-speed transmission channel at frequencies to 70 GHz. That provided the S-parameters needed to assure accurate de-embedding , which removes the effects of the channel from measurements. De-embedding lets engineers prove that the SerDes met published specifications.

See more DesignCon 2019 Coverage

- Mathworks, SiSoft Announce First Products Following Acquisition (EE Times)

- DesignCon 2019: PAM4 makes everything harder (EDN)

- 112G Digs in at DesignCon 2019 (eeWeb)

Related articles:

- DesignCon 2019: PAM4 makes everything harder

- De-embedding improves measurement accuracy

- 400G Ethernet is Here, as are Other Speeds

- PAM4, error correction bring 400GbE test challenges

- Forward Error Correction

- PAM4: A new measurement science

- The difference between BER and BER

- Using BER testing as a troubleshooting tool

Advertisement

Learn more about Electronic Products Magazine