By Richard Quinnell, global managing editor for the AspenCore Network

The RISC-V (pronounced “risk-five”) Foundation is attracting widespread industry interest thanks to its open-source architecture with the advantages of standardization and core specifications on the verge of ratification. In addition, soft and hard CPU cores along with chips, development boards, and tools are commercially available, and major companies have started adopting RISC-V to replace their custom architectures.

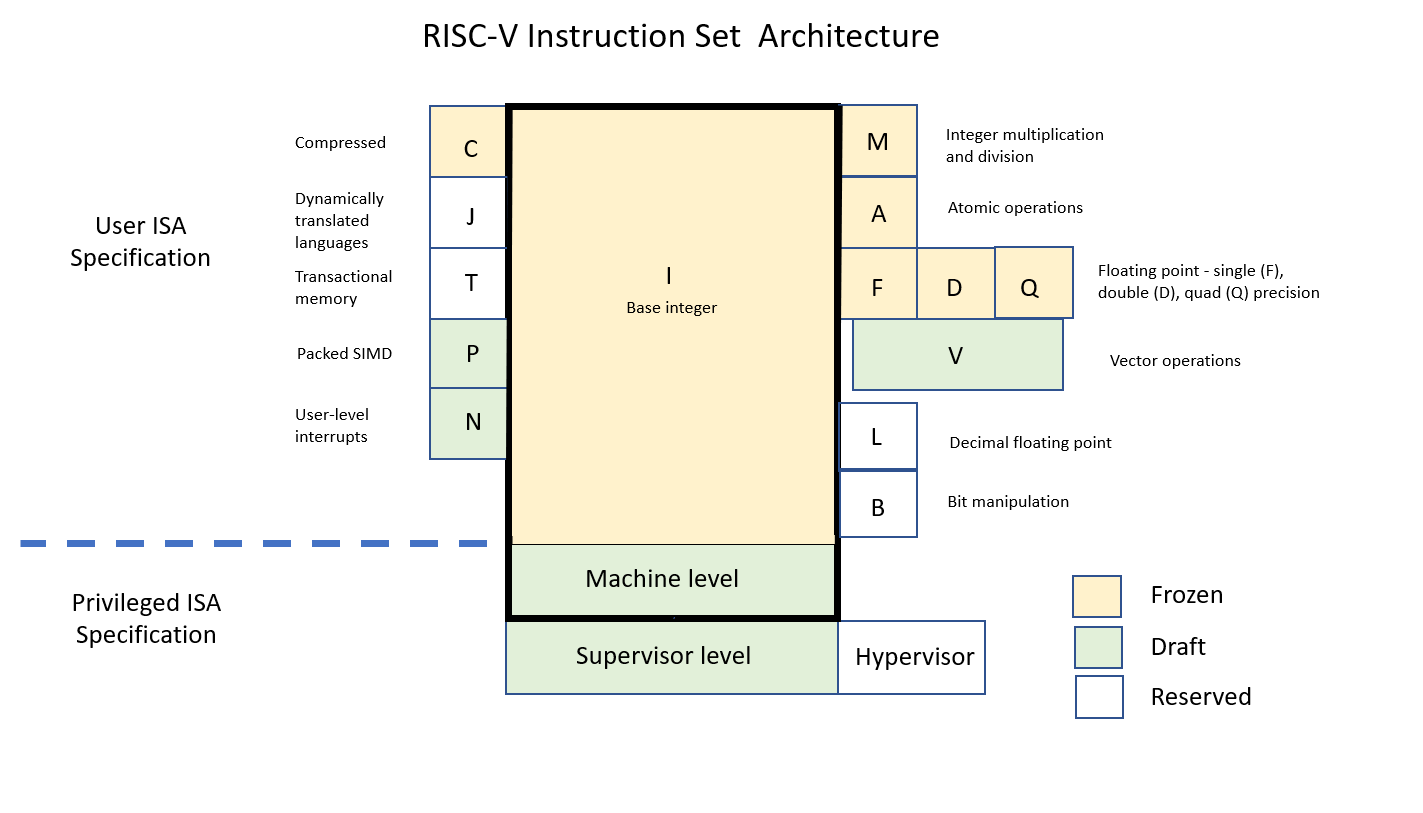

A key feature in the architecture’s appeal is that CPU developers can adapt RISC-V functionality to their needs without sacrificing the applicability of tools and libraries created for the base standard. The key to that adaptation lies in understanding RISC-V’s modular instruction set architecture.

RISC-V started as the fifth iteration of reduced instruction set computing (RISC) design efforts at UC Berkeley but quickly evolved from academic research to a movement seeking to redefine the electronics industry’s processing hardware design approach. Currently, system developers must either choose a proprietary CPU architecture, often optimized to a specific application space, or design their own CPU architecture. By pursuing their own design, however, developers give up the extensive support ecosystems that established CPUs have developed. There is a compromise: adapting a proprietary CPU architecture to gain customization while retaining much of the support ecosystem. This compromise, unfortunately, is impractical for many design teams due to high architecture licensing fees for proprietary architectures.

The RISC-V initiative seeks to offer designers an alternative that permits customization and innovation while retaining many benefits of standardization. To do so, the RISC-V Foundation maintains and drives community development of the modular, open-source, RISC-V processor instruction set architecture (ISA), which aims to meet application needs spanning embedded systems to server farms and beyond. The architecture’s specifications are free to download, and developers are free to implement designs based on the ISA without paying a license fee. Nor are they obligated to make their designs available to others, as with some open-source initiatives. It is the ISA that is open-source; individual designs, hardware architectures, and customizations can remain proprietary if developers wish.

The initiative has gained considerable momentum. There are now RISC-V chips and cores available, both commercial and open-source. Companies like SiFive, GreenWaves Technologies, and Microsemi have development boards for their RISC-V implementations. Development tools, software libraries, and operating system ports (including Linux) are all part of the current RISC-V support ecosystem. Leveraging all of this support for a custom design, though, begins with a close look at the RISC-V ISA’s structure.

Click here for the complete article published at EDN.

For more in-depth insight into technical and business aspects of RISC-V, check out these other articles in this AspenCore Special Project.

Advertisement

Learn more about Electronic Products Magazine