By Maurizio Di Paolo Emilio, editor, Power Electronics News

In most current devices, silicon-based CMOS chips are used for computing. Silicon in advanced communications systems is driven to its limits — limits that translate into thermal problems. This is why the current 5G mobile devices on the market become very hot during use and turn off after a short time.

Various organizations, including IBM, the Hong Kong University of Science & Technology, and MIT, have been experimenting with integrating silicon with compound semiconductors to get around such problems.

The electronic devices of the near future will have to contain sensors and transmit data wirelessly to a control center (possibly communicating over a 5G network). This means that they will have to combine RF, low operating power, and a small form factor. A clean and promising approach to achieve all these objectives is to create single chips that combine the capabilities of silicon CMOS with III-V semiconductors.

These materials combine elements in the 3rd and 5th columns of the periodic table; examples include gallium nitride (GaN) and indium gallium arsenide (InGaAs). Thanks to their unique properties, they are exceptionally suitable for optoelectronics (LEDs) and communications (5G), thus increasing the overall efficiency of the system.

Chips and 5G networks

5G is not simply a faster 4G. Networks running 5G will be up to 20 times faster than the existing 4G network, enabling video download speeds up to 10 times faster. 5G is considered a “new” web, the infrastructure candidate for managing the Internet of things (IoT).

The 5G network will lead to sophisticated cloud app services, an intelligent and connected society with smart cities, self-driving cars, and new industrial platforms. There's an imperative to build the ICs necessary to enable all of that, but there is still a lot of design work to do and test & measurement to perform. Among the most challenging obstacles are the ongoing evolution of the standards, the adoption of millimeter wave (mmWave) technology, and controlling costs.

The Singapore-MIT Alliance for Research and Technology (Smart) , MIT’s Research Enterprise in Singapore, has announced the successful development of a commercially viable way to manufacture silicon circuitry integrated with high-performance III-V devices.“Most current devices use silicon-based CMOS chips that are used for computing, but they are not efficient for illumination and communications. This results in low efficiency and heat generation,” said Fayyaz Singaporewala, senior innovation manager of the Low Energy Electronic Systems (LEES) Interdisciplinary Research Group at Smart.

The power density of GaN technology has made it a turning point for the industry, and the number of such devices used in phased array applications and other domains is increasing. Finally, the price is reaching a level that makes the technology attractive even to the budget-conscious consumer market. These technologies have the potential to combine high-speed converters with microwave components in a single die, including power amplifiers and biasing circuits.

“Silicon CMOS technology can achieve power-added efficiency (PAE) of ~20% while GaN devices can achieve PAE of 50% or more. But silicon CMOS technology has the advantage of higher integration of added functionalities (such as on-chip digital control, adaptive matching, digital pre-distortion etc). Smart's technology allows us to leverage the best of both these worlds which is critical for 5G technology,” said Kenneth Lee, senior scientific director of the LEES group at Smart.

5G must provide not only the highest data rates but also a latency of less than 1ms. Due to the properties of Internet protocols, lower latency is essential to achieve higher data transfer rates. In a car, where it’s important to exploit communication for safety, in particular, to drastically reduce the chances of fatal accidents.

“The new devices will enable 5G devices to be a working reality as current technology cannot keep up with the requirements of 5G. Our technology will allow chips that can meet all applicable specifications of 5G within the tight power and space budgets of complex mobile devices that are coming up. Silicon III-V chips will enable the creation of the mobile 5G devices that will power cars, mobile devices etc, and would accelerate the adoption of 5G,” Lee said.

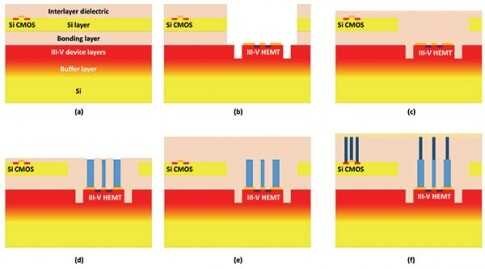

The technology is based mainly on two layers of silicon and III-V materials on separate substrates, together in a 1-micron stack. The process can use existing production tools with a decisive reduction in costs and high-performance electronic systems. An overview of the LEES processing scheme is shown in Fig. 1 .

Fig. 1: (a) A 1 µm-thick silicon CMOS layer is bonded to a III-V-on-silicon wafer, fabricated using epitaxy. (b) Windows are opened in the CMOS-free areas to expose the underlying III-V layers, and III-V devices are then fabricated. (c) The dielectric layer is deposited. (d) W-plugs are created to contact III-V devices. (e) The dielectric is deposited and flattened using chemical-mechanical polishing. (f) The silicon foundry connects the silicon CMOS and III-V devices together by typical interconnections to complete the integration process.

Smart LEES has a thermal/reliability group dedicated to studying the thermal profile of its chips and devising robust thermal management solutions. The control of the III-V device layout allows the creation of thermally-efficient devices, and CMOS + III-V integration design rules have also been established to mitigate thermal problems. “Our thermal/reliability group”, said Lee, “has also developed front- and back-side thermal spreading/heat extraction technologies to reduce hotspots and allow for cooler device operation.”

The hybrid circuits would also be able to operate with better stability and less noise, with a consequently significant increase in the functionality, complexity, and performance of the circuit, all achieved without having to reduce the size of the device or increase the transistor count.

Currently, Smart's research focuses on two families of III-V materials: the nitride family, which is aimed at high-power applications and blue and green LEDs; and the arsenide-phosphide family, intended for applications such as very high-frequency power amplifiers, low-noise amplifiers, and yellow and red LEDs.

A challenge was how to approach the CMOS silicon layers and the III-V materials. The success comes from the fabrication of silicon CMOS devices first, to the point just before the back end interconnection, so that an interlayer dielectric covers the silicon CMOS transistors.

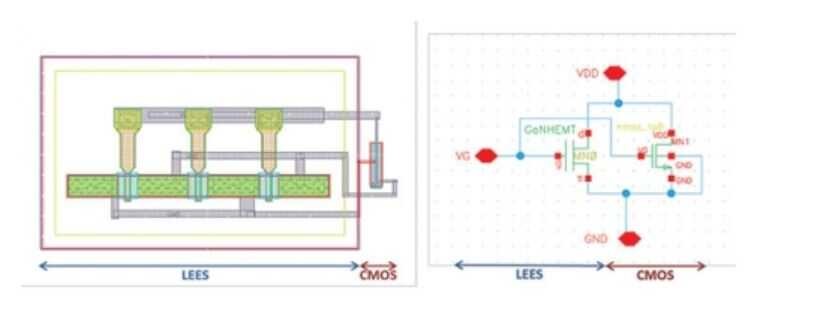

Subsequently, the wafers are transferred to the Smart structure for integration and III-V processing. The transfer of the silicon CMOS layers on each wafer to the III-V ones involves a series of wafer bonding, oxide deposit, and chemical-mechanical polishing phases. The bond is made with a direct and improved fusion process through subsequent annealing (Fig. 2 ).

Fig. 2: SMART has developed a series of CAD tools for implementing these new chips

Conclusion

“Silicon semiconductors revolutionized the electronics industry and continue to dominate in the microprocessors and memory segments. III-V semiconductors have the potential to revolutionize the industry again and enable a wide range of innovation, from 5G to IoT and smart vehicles. Compound semiconductors have diverse properties that will benefit these applications. Key among them is the significantly higher power efficiency and unique optical properties something that silicon struggles to achieve,” said Singaporewala.

Smart estimates the 5G and lighting markets have a combined market potential of over $100 billion.

“However, to unlock this vast potential, integration into the silicon world is essential. Leveraging the optimized efficiency of silicon design and manufacturing, using the elegant integration methodology developed by LEES, III-V devices will be able to transform current applications into system-defining next-generation products. In addition, this novel monolithic integration will spark a new wave of ‘blue ocean’ applications as designers express themselves using a broad palette of devices,” said Lee.

GaN is more power-efficient than silicon for 5G RF. Many companies are organizing to develop products with GaN-on-silicon technology in RF market also outside the mobile sectors, wireless base stations, and related applications for commercial telecommunications infrastructures. MACOM and STMicroelectronics are working on 150-mm GaN-on-silicon production for the worldwide 5G Telecom buildout.

The article originally published at sister publication EE Times.

Advertisement

Learn more about Electronic Products Magazine