Less than two years after testing a 7-nm chip, IBM and its Research Alliance partners, GlobalFoundries and Samsung, have developed and tested a silicon-nanosheet transistor architecture to enable 5-nm chips. The architecture uses horizontal gate-all-around FETs (GAAFETs) instead of the vertical FinFET gate structure.

Devices built with GAAFETs could fit 30 billion transistors on a chip, up from 20 billion transistors on a chip built with 7-nm FinFETs, said the researchers. The resulting performance increase would speed data-intensive applications such as cognitive computing and the Internet of Things. Smartphone and other mobile device batteries could run for two to three days on a full charge.

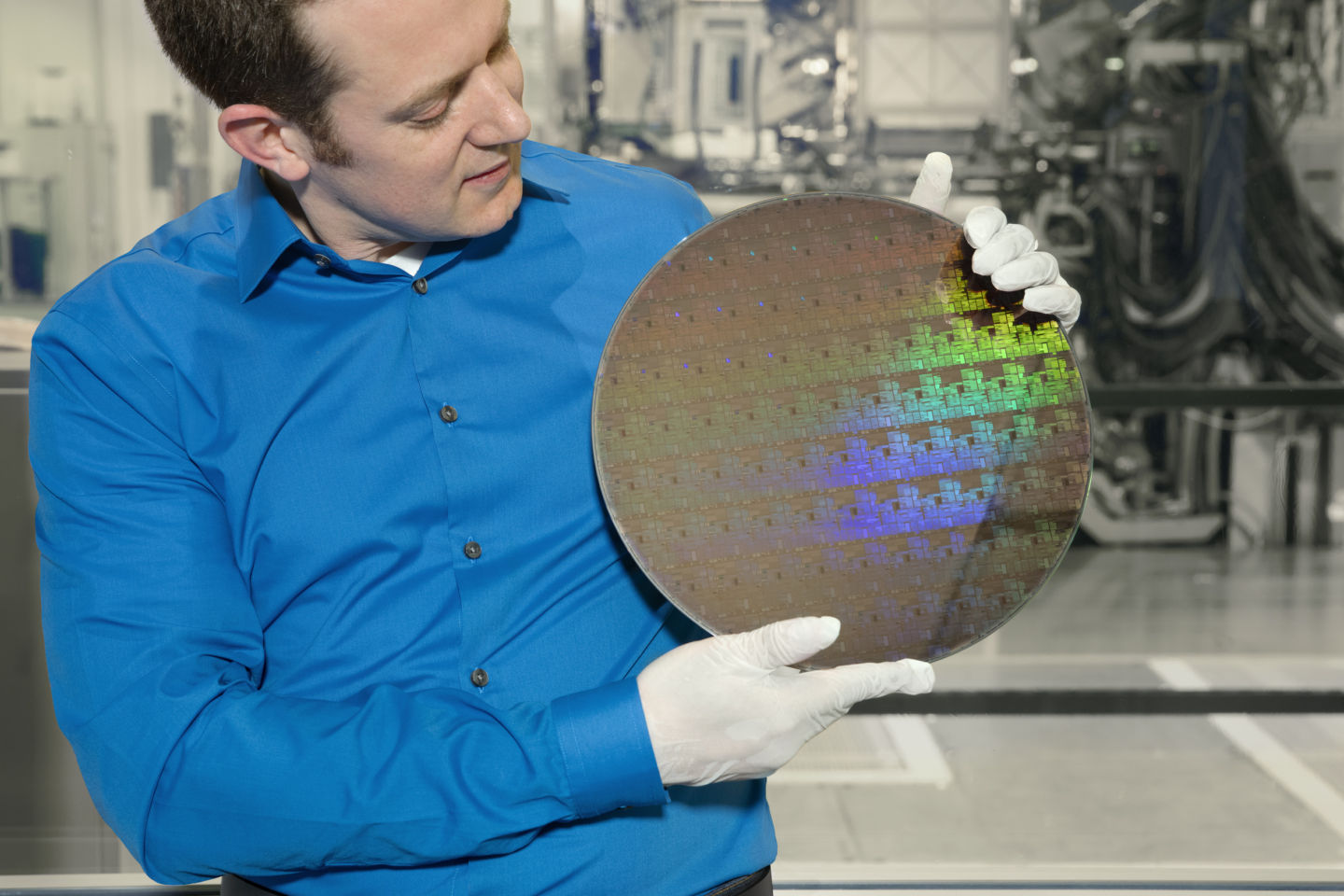

The team used extreme-ultraviolet lithography to produce the 5-nm test chips. EUV allows the nanosheet width to be adjusted continuously within a single chip design, meaning that circuits can be optimized for power and performance in one manufacturing process. IBM states that 5-nm chips built with the architecture would enable a 40% performance increase at the same power or a power savings of 75% for the same performance compared with the 10-nm chips currently in production.

Tri-gate FinFETs have been used since the 22-nm process generation but are expected to run out of steam around 7 nm. The alliance partners believe that GAAFETs will be viable down to 3 nm when combined with EUV. What will come after 3 nm remains unknown.

“As we make progress toward commercializing 7 nm in 2018 at our Fab 8 manufacturing facility, we are actively pursuing next-generation technologies at 5 nm and beyond to maintain technology leadership and enable our customers to produce a smaller, faster, and more cost-efficient generation of semiconductors,” said Gary Patton, CTO and Head of Worldwide R&D at GlobalFoundries, in a release.

The partners demonstrated the 5-nm chips at the SUNY Polytechnic Institute Colleges of Nanoscale Science and Engineering’s NanoTech Complex in Albany, New York. Detailing their research in Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET , they suggest that 5-nm chips are not just possible and powerful but are on the horizon.

Advertisement

Learn more about Electronic Products Magazine