By Majeed Ahmad, contributing editor

After sitting on PCI Express (PCIe) 3.0 for nearly seven years, the industry is finally ready to move on to the next high-speed interconnect version: PCIe 4.0. It doubles the I/O performance and takes the speed to 16 Gbps while running four lanes concurrently.

It’s worth mentioning here that the PCIe 4.0 specification isn’t merely an extension of the PCIe 3.0 interface technology. Instead, PCIe 4.0 marks a bandwidth transition to accommodate data center and high-speed consumer applications such as 4K streaming.

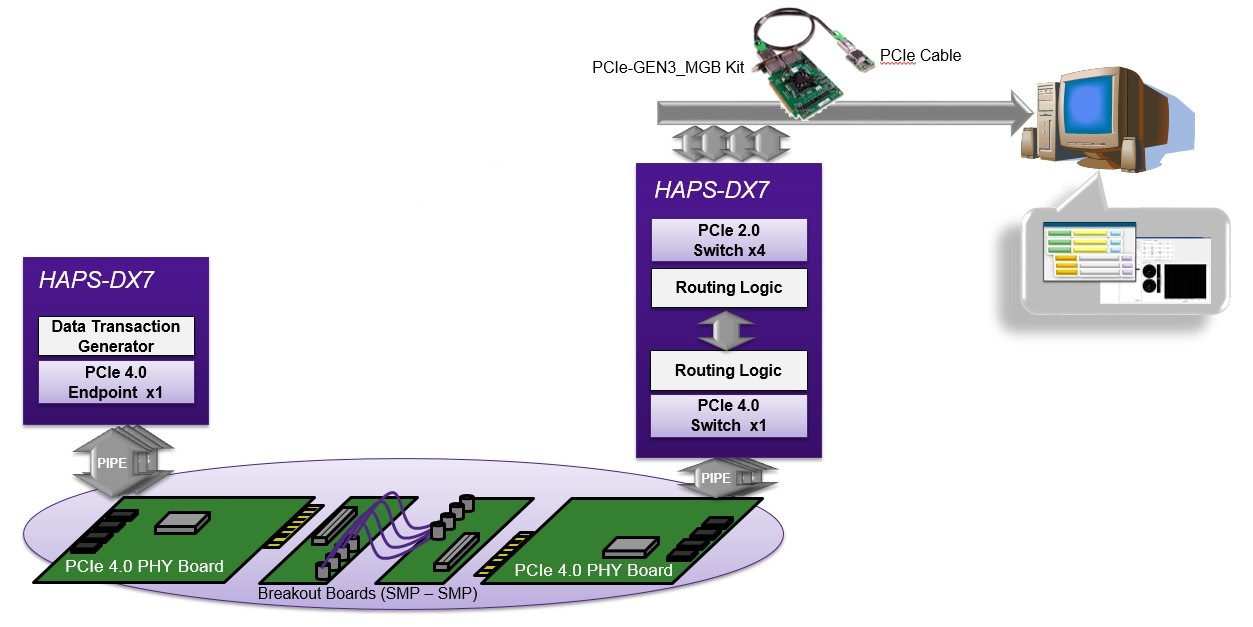

Image: Synopsys.

The PCIe 3.0 interconnect was not able to keep up with the latest Ethernet specs without increasing the number of lanes. And an increase in the number of lanes meant higher cost in terms of power, circuit board layout, and required components.

The PCI Gen 4 technology also allows the next-generation server, storage, and networking equipment to analyze data more effectively and find insights in real time.

PCIe 4.0 demos

After the release of the Revision 0.9 specification, we see a stream of PCIe 4.0-enabled products. Here, two recent product developments are worthwhile to mention. First, Rambus has joined hands with interface IP supplier PLDA and verification IP firm Avery Design Systems to create a pre-verified PCIe 4.0 subsystem (shown below).

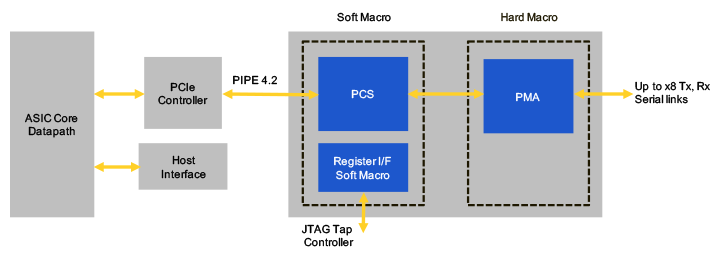

Image: Rambus.

It’s a silicon-proven solution that includes a Rambus SerDes PHY, a PLDA PCIe controller, and Avery Design’s verification IP. And it allows designers to quickly incorporate these pre-verified and validated PCIe 4.0 building blocks in their chipset solutions for networking, data center, and other high-throughput data applications.

Second, Cadence has announced the availability of a 16-Gbps PHY IP designed on TSMC’s 16FF+ process and has demonstrated its interoperability with Mellanox’s PHY IP for PCIe 4.0 architecture. Again, it’s aimed at bolstering the ecosystem around the embryonic PCIe Gen 4 technology.

And while the ecosystem of PCIe Gen 4 continues to evolve in order to support a wide array of vertical markets, there is an increase in the chatter about the PCIe Gen 5 bus, which boasts a whopping 32-Gbps speed.

The industry observers anticipate that version 10 of the Gen 5 specification will be ready by 2020. For now, however, Gen 4 is coming along quickly, and PCIe 4.0 boards are expected to arrive on the market next year.

Advertisement

Learn more about Electronic Products Magazine