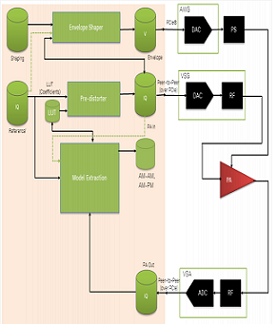

The following is a block diagram of the Keysight M9451A PXIe Measurement Accelerator with DPD personality and the interfaces to the other test equipment in the system:

The highlighted box shows the key functions of the digital pre-distortion (DPD) and envelope tracking (ET) gateware in the M9451A PXIe measurement accelerator. The data cylinders are allocated blocks of IQ data in the M9451A memory. The rectangles represent algorithms implemented in the accelerator. The test software controls how data is processed by passing data handles associated with each data cylinder to the API method associated with each algorithm rectangle. Peer-to-peer (P2P) PCI Express® technology is used to achieve fast data transfers between the M9451A memory and the M9381A PXIe vector signal generator (VSG) hardware.

The ideal reference waveform, without pre-distortion, is first loaded into the M9381A PXIe VSG ARB memory and then transferred to the M9451A using P2P. After the model extraction algorithm computes a lookup table (LUT), or other coefficients, the pre-distorter creates a pre-distorted waveform in the PA In cylinder.

P2P is used to transfer the pre-distorted waveform data to the VSG ARB memory. P2P PCI Express technology is also used to transfer measurement data from the M9391A or M9393A PXIe vector signal analyzer hardware to the M9451A hardware.

Click here for additional information

Download full block diagram below

Advertisement

Learn more about Keysight Technologies, Inc.