Microsemi Corporation (Nasdaq: MSCC), a leading provider of semiconductor solutions differentiated by power, security, reliability and performance, announced the company’s new Mi-V™ ecosystem with industry leaders, to increase adoption of its RISC-V soft central processing unit (CPU) product family. The announcement comes as the company also introduces Mi-V RV32IMA and additional field programmable gate array (FPGA)-based soft CPU solutions ideally suited for designs utilizing RISC-V open instruction set architectures (ISAs).

“As a leader in RISC-V, we are pleased Microsemi is the first tier one vendor to build out a complete open RISC-V ecosystem, which not only supports our needs, but contributes to the entire development community,” said Jim Aralis, chief technology officer and vice president of advanced development at Microsemi. “Customers can now select RISC-V for their new designs knowing a tier one vendor committed to the success of this technology is providing all the necessary tools to confidently use RISC-V soft CPUs in their products.”

RISC-V, an ISA which is a standard open architecture under the governance of the RISC-V Foundation, offers numerous benefits, including portability as well as enabling the open source community to test and improve cores at a faster pace than closed ISAs. As the RISC-V intellectual property (IP) core is not encrypted, it can be used to ensure trust and certifications not possible with closed architectures. Microsemi’s new Mi-V ecosystem brings together a number of industry leaders involved in the development of RISC-V to leverage their capabilities and streamline RISC-V designs for customers.

“Micrium is pleased to join Microsemi’s Mi-V ecosystem with our highly dependable uC/OS-II real-time kernel, a full-featured embedded operating system,” said Jean Labrosse, co-founder and chief architect at Micrium. “As RISC-V continues to grow in popularity, we look forward to working closely with Microsemi to support accelerated adoption of its RISC-V soft CPU product offerings as well as the entire ecosystem’s RISC-V advancements.”

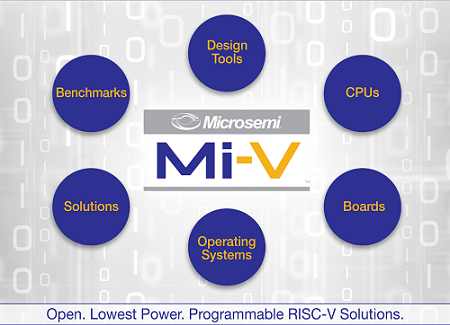

Microsemi’s Mi-V ecosystem, part of Microsemi’s Accelerate Ecosystem, contains a number of components. Design tools include Microsemi’s SoftConsole Eclipse-based integrated development environment (IDE), the firmware catalog and Libero PolarFire system-on-chip (SoC). Operating systems include Express Logic’s ThreadX, Huawei LiteOS and Micrium µC/OS-II. Boards include the RTG4™ development kit, IGLOO™2 RISC-V board from Future Electronics, PolarFire Evaluation Kit and more. Debug dongles from Microsemi and Olimex, first-stage bootloaders and numerous soft peripherals are also included. Example projects, drivers and firmware are all available on GitHub, the world’s largest repository of open source software.

Deployment of soft CPUs implemented with the R11C-V ISA is automatic and delivered to the user’s desktop via Microsemi’s IP Catalog. No end user license agreements are needed to gain access to the soft CPUs. Using RISC-V soft CPUs within the Mi-V ecosystem is simple, easy and free.

“Express Logic is pleased to be a foundational part of Microsemi’s Mi-V RISC-V ecosystem,” said William E. Lamie, President, Express Logic. “Our X-Ware Internet-of-Things (IoT) platform, including the industry-leading ThreadX RTOS with over 6.2 billion deployments, is the preferred embedded software platform for all designs requiring industrial-grade run-time solutions—making us an ideal fit for this new consortium.”

Offering low power and an open architecture, Microsemi’s PolarFire™, RTG4™, SmartFusion™2 and IGLOO™2 field programmable gate array (FPGA)-based RISC-V soft CPU cores are ideal for developing a wide variety of applications within the aerospace and defense, industrial and security markets. The Mi-V soft CPU cores make them particularly suitable for applications including guided munitions, IoT, secure communications and wireline bridging.

“The open source, royalty-free RISC-V instruction set creates a new business model for CPU designers that is garnering increasing interest and support,” said Linley Gwennap, principal analyst with The Linley Group, which named the RISC-V ISA “Best Technology of 2016” at its annual Analysts' Choice Awards in January 2017. “By introducing the RV32IM CPU core with support from the Mi-V ecosystem, Microsemi will play an important role in boosting the adoption of RISC-V.”

Through Microsemi’s early involvement in the creation of the RISC-V Foundation, the company has an established leadership role in the emerging standard and ecosystem and is working closely with the nonprofit to ensure the ISA becomes an industry standard for a wide variety of computing devices. Ted Speers, head of product architecture and planning for Microsemi’s Programmable business unit, was appointed to the inaugural board of directors of the RISC-V Foundation in July 2016, and Ted Marena, director of SoC FPGA marketing, was recently sworn in as chair of the RISC-V Marketing Committee after serving as vice-chair since August 2016. Marena will also be the featured speaker at EE World Online’s upcoming webinar titled, “The RISC-V ecosystem is ready for prime time. Get started here!” on Oct. 25, 2017. Attendees can register online to join this event.

The Mi-V Ecosystem began as part of the Microsemi Accelerate Ecosystem, a program designed to reduce time to market for end customers and time to revenue for ecosystem participants. Microsemi's Accelerate Ecosystem brings together leading silicon, intellectual property (IP), systems, software and design experts to deliver solutions for end customers. Learn more at http://www.microsemi.com/design-support/accelerate-ecosystem-partners.

Advertisement

Learn more about Microsemi