Developed for greater design flexibility and scalability, NXP Semiconductors has unveiled its MCX portfolio of microcontrollers (MCUs), targeting industrial and IoT edge applications, including smart homes, smart factories, and smart cities. The four new series of 32-bit MCUs, built on a common platform, focus on different features and functionality from ultra-lower power to advanced performance, enabling developers to select the best device for their applications.

The MCX portfolio is developed around the foundation of meeting key challenges in IoT edge design: advanced security, lower power requirements, real-time performance, and connectivity in combination with keeping up with fast-changing technology. It’s also built on a common platform for easy migration and faster development.

The MCX families are based on high-performance Arm Cortex-M cores and integrate a full set of peripherals for design flexibility. The devices feature up to 4 MB of on-chip flash memory, low power cache, and advanced memory management controllers, as well as up to 1 MB of on-chip SRAM to enhance real-time performance of edge applications.

Built using NXP’s security-by-design approach, the MCX devices offer secure boot with an immutable root of trust, hardware-accelerated cryptography, and, on select families, a built-in EdgeLock secure subsystem.

“The complete MCX series are based on the single Cortex-M33 core so users can move up and down the different series as they grow and require the performance, or if they don’t need the extra performance, they can go back to the entry level or essential levels,” said CK Phua, product manager MCUs at NXP.

Leveraging the best features of the NXP’s LCP and Kinetis MCU families, the MCX portfolio expands the capabilities and scalability, including more memory and lower-power options, simplifies system design, and keeps the MCUXpresso suite of software and development tools to give users a good experience as they start developing their software, said Phua.

The new series is a combination of the Kinetis and the LPC MCU families, together with architecture improvements to achieve the performance and low-power requirements needed for these edge applications, he added.

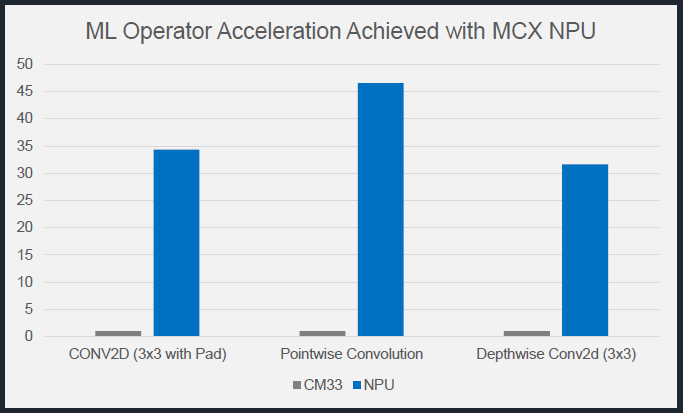

NXP’s MCX portfolio of MCUs include the high-performance MCX N series, analog-focused MCX A series, MCS W series for low-power wireless connectivity, and the ultra-low–power MCX L series. The MCX N features the first instantiation of NXP’s new neural processing unit (NPU) for accelerating inference at the edge, delivering up to 30× faster machine-learning (ML) throughput compared with a CPU core alone.

The MCX NPU delivers over 30× relative acceleration for basic ML operations when compared with the Cortex-M33 core. (Source: NXP Semiconductors)

Four series

One of the key benefits of the new MCX portfolio is its flexibility in memory, performance, features, power, and compatibility. The series scales up to 4 MB of flash on-chip and 1-MB SRAM, along with scaling performance features and functionality, while offering lower-power modes and pin-to-pin compatibility options.

One microcontroller can’t do everything, so the MCX portfolio offers four sub-series, said Phua.

The highest-performance series is the MCX N Advanced series, with a 150- to 250-MHz Arm Cortex-M33 core. Designed for secure and intelligent applications, this advanced series comes with an integrated EdgeLock secure subsystem and dedicated NPU to deliver a high-efficiency compute architecture for real-time inference.

The high-performance MCX N series offers a broad range of peripherals, including an NPU and DSP that supports specific requirements, like audio or some other filtering function, and adds the EdgeLock secure subsystem to ensure the customer’s end products are secure through their chain, Phua said.

The MCX A Essential series (46 to 96 MHz) meets the broad market for more cost- and space-constrained applications as well as lower pin-count requirements, he said. This includes applications such as motor control in which cost, advanced analog capabilities, and fast time to market are key considerations. On-chip features include high-performance ADCs, comparators, DACs, and instrumentation-class op amps.

The MCX W Wireless series (32 to 150 MHz) offers low-power narrowband connectivity, including Bluetooth Low Energy (LE), and is designed to simplify wireless connectivity for IoT devices. It features an energy-efficient radio to help extend the battery life of small, connected systems.

The MCX W with wireless Bluetooth LE offers “quite a bit of on-chip integration to support external bill-of-materials reduction,” said Phua.

The MCX L Ultra-Low Power series (50 to 100 MHz with boost option), designed for power-critical applications, focuses on battery-operated applications, “achieving the lowest active power and lowest leakages to squeeze every drop from the battery,” added Phua. They are designed to help extend battery life significantly compared with traditional MCUs.

The offering is supported by the MCUXpresso suite of development tools and software and enables developers to reuse software across the portfolio for faster product development. It also enables easy migration and the ability to scale up or down with software reuse. The developer-focused software also includes both RTOS and middleware options.

“This also preserves our existing customers’ engineering investment [enabling them to port existing code to the MCX platform without redesign] for those who have been using LPC and Kinetis MCUs,” said Phua. [It is meant] “to give the users a common platform so that they can move up and down the various series and also speed up the development.”

ML and run-time inference will be supported by NXP’s eIQ ML software development environment. Developers can use the eIQ tools to train ML models targeting either the NPU or the CPU core and deploy them on the MCU.

ML acceleration

The high-end MCX N Advanced family includes an integrated NPU for ML acceleration, which leverages an internal NXP design.

“We’ve opted to do that versus a third-party IP because a lot of the available IP cores in the market did not scale down to the level that we wanted to enable both power and cost efficiency,” said Ali Osman Ors, director of AI ML strategy & technologies at NXP.

The NXP-designed architecture scales from 32 operations per cycle up to 2,000 operations per cycle, with potential for future expansion, he added.

All of the family members can run ML workloads on the Cortex-M33 main CPU if needed, said Ors. But for applications around anomaly detection, predictive maintenance, and various levels of voice-based ML, these can be done more efficiently on a dedicated accelerator like the NPU, he added.

“Anytime you have more need for machine-learning capacity, that’s where you benefit the most from leveraging the MCX N family with the integrated NPU, and, of course, if your machine learning is only a small fraction of your overall application, you can always just leverage the Cortex-M33 itself,” said Ors. “It’s still capable of running those operations.

“We’ve been part of the TinyML movement as well,” he added. “While a lot of announcements are made on the higher end, like autonomous vehicles and application processors and high-end server-grade ML and AI, where it is really getting into the homes and the industrial space is in the microcontroller domain, so we’re offering that option to our customers to scale up if they have ML needs. They can go from an MCX A family into the MCX N family and get an additional boost of machine-learning workload capacity.”

NXP will offer samples of the MCX N and MCX W series devices by the end of 2022, followed by evaluation kits in the first quarter of 2023. Launch dates are still being planned for the MCX A and MCX L series. The MCX MCUs will be available in several package options, from TSSOP to BGA with 16 to 200 pins.

The company will demonstrate the MCX W series at Embedded World 2022, June 21–23, in Booth 4A-222. The MCX N chip also will be showcased.

Advertisement