With few exceptions, today’s generation of radars employ a phased array or active electronically steered array (AESA) architecture to improve reliability and accuracy, and to allow tracking of multiple targets. This approach replaces the single, high power tube and mechanically rotated parabolic antenna and its inherent single point of failure, with a large array of transmit-receive modules that employ high performance ASICS and power transistors.

NXP has an extensive portfolio of LDMOS (and soon to be GaN) transistors supported by a strong portfolio of SiGe:C based discretes and ICs for L and S band radar systems. In addition, our catalog of high speed dataconverters, employing traditional interfaces as well as JESD204A/B serial interfaces, is well suited for analog, digital and hybrid beamforming implementations. The JESD204B interface standard, specifically, really shines in digital beamforming systems, minimizing board space, BOM cost, engineering time, and FPGA interface complexity.

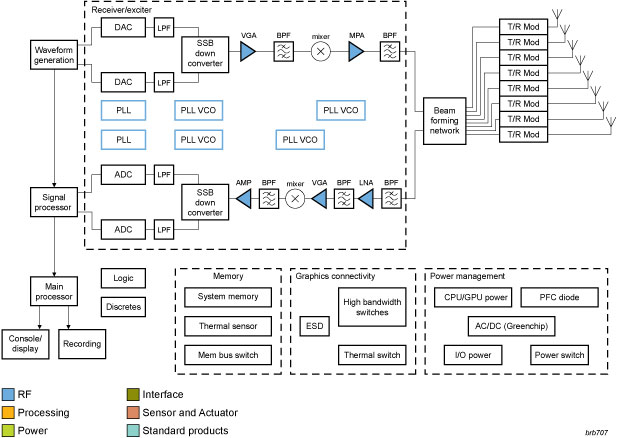

Download Full Block Diagram Below

Advertisement

Learn more about NXP Semiconductors