By Gina Roos, editor-in-chief

The RISC-V initiative continues to make gains in delivering new commercial and open-source chips and cores. The latest comes from a partnership between X-FAB Silicon Foundries and Efabless Corp., a crowd-sourcing IC platform, announcing first-silicon availability of the Efabless RISC-V system-on-chip (SoC) reference design. Efabless successfully bench-tested Raven , the mixed-signal SoC, at 100 MHz, and based on its simulations, it expects the design to operate at up to 150 MHz.

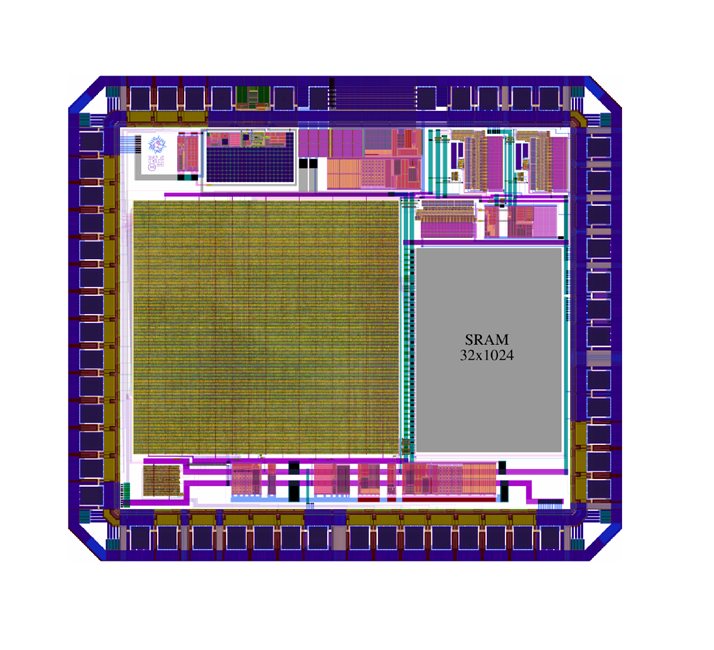

Developed in less than three months from design start to tape-out, using the Efabless design flow based on open-source tools, the Raven SoC is based on the community-developed ultra-low-power PicoRV32 RISC-V core. “Nearly 75% of Raven’s die area is covered by X-FAB standard library blocks and macros,” said Ulrich Bretthauer, product marketing manager at X-FAB, in a statement. “Using these proven IP blocks increased the reliability of the Raven while minimizing first-silicon risk.”

What makes the SoC unique, according to the companies, is that its open-source top-level design uses X-FAB’s proprietary analog IP and is created using an open-source design flow. So what the hybrid design offers is open innovation while protecting proprietary IP investments.

The SoC is manufactured on X-FAB’s high-reliability XH018 180-nm, six-metal process . It offers a variety of options, including a low-power option, on-chip isolation for high voltages, and high-temperature flash memory. In addition, the XH018 process meets automotive quality requirements and is also used in industrial and medical applications.

The semiconductor design is fully functional, and Efabless is working with first customers on derivative offerings. Raven is available from the Efabless marketplace as a reference design without a license fee.

If you’re looking for additional resources to get started, X-FAB offers a series of free webinars . Design kits and PDKs for open-source IP designs are also available.

Advertisement

Learn more about Electronic Products Magazine