This post sponsored by Texas Instruments.

Programmable logic has been around since the days when new 8-bit microcontrollers were flourishing. And while 8-bit microcontrollers are still flourishing, the simple programmable logic of yesteryear is not.

Programmable Read-Only Memory (PROM) was the first field-programmable logic element created to allow early microcontrollers, sequencers, and bit-slice machines to retain a non-volatile programmed functionality. Successive Integrated Fuse Logic (IFL) and Integrated Logic Sequencers (ILS) were the first field-programmable fusible-link-based logic replacement parts that could absorb the functionality of a dozen or so discrete logic parts.

A simplified iteration of the IFL reduced the logic depth to retain the sum of products functionality and the resulting Programmable Logic Arrays (PALS) were born. These typically implemented a single level of combinatorial logic with or without registered outputs.

As densities improved, programmable logic devices evolved into macro-cell arrays, logic element arrays, and several other terminologies to represent discrete chunks of replicated logic spread around a die, and separated by standard or specialized routing resources. As the depth and complexity increased, the term Complex PLD or CPLD arose to differentiate between the simple sum of product devices and more sophisticated macro-cell (or lookup table)-based logic block parts.

The unfolding of the PLD’s turnaround is an interesting story. It used to be that PLDs became popular to support microcontrollers by absorbing discrete logic and letting engineers consolidate address decoding for memory and I/O partitioning onto a single chip. Now, FPGAs can hold more than one instantiation of a microcontroller or microprocessor along with standard and custom peripherals crafted from the gate level.

In the beginning, power was typically not an issue. The micro, peripherals, drivers, and PLDs would operate from the same Vcc levels. Energy management was in its infancy since these solutions were already lower-power alternatives to boards of discrete logic chips. However, power became more of an issue when macro-cells started to become differentiated cells.

For one thing, lower-power micro cores emerged with even lower-power sleep and suspend modes. This situation cried out for a more flexible controlled-power solution instead of the one-size-fits-all approach. Altera’s Arria V FPGAs illustrate this point. The Arria V FPGAs are mid-range parts. They are more dense and functionally intensive than Altera’s MAX and Cyclone families, and less dense than the company’s Stratix FPGA family.

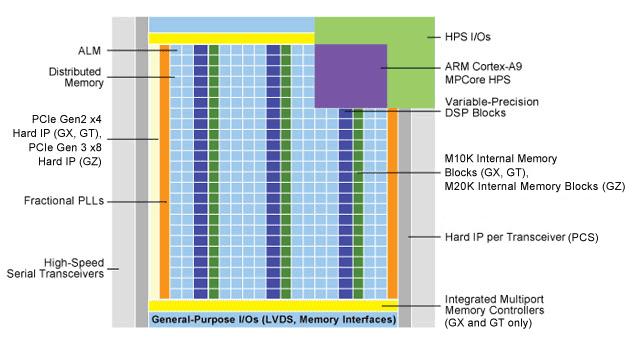

However, their five variants include configurations with dual-core ARM Cortex A9 processors, several PLLs, DSP function blocks, embedded memory, PCI express, and a variety of copper- and fiber-based banks of transceivers (Figure 1). For example, one part can house up to 36 12.5 Gbit/sec transceivers.

Figure 1: As programmable logic devices mix hard-peripheral macros with more sophisticated soft macros, the need for dynamic power control becomes more evident. With hundreds of I/O lines and logic blocks that engage and disengage with hot swaps and mode changes, dynamic control becomes a must. (Source: Altera)

Figure 1: As programmable logic devices mix hard-peripheral macros with more sophisticated soft macros, the need for dynamic power control becomes more evident. With hundreds of I/O lines and logic blocks that engage and disengage with hot swaps and mode changes, dynamic control becomes a must. (Source: Altera)

In addition, these are very large parts with a lot of I/O; in some cases over 500 General-Purpose I/O lines (GPIO) that can operate with different logic levels and current strengths as well as in LVDS modes. As one might imagine, it is necessary for the power of the FPGA to become a more dynamic function as opposed to single regulated inputs, especially when hot-swap functionality is added to the fray. And, the best solutions occur when the FPGA and power subsystems work together to reduce overall heat and power, and possibly to extend battery life if battery powered.

Texas Instruments™ provides a power solution for the Altera Arria V FPGAs in the form of the PMP9357 reference design, which makes the power subsystem a controlled peripheral capable of performing dynamic regulation, metering, and monitoring of power.

The Altera Arria V GZ FPGA Discrete Power Solution Reference Design uses the company’s TPS54620 synchronous step-down converters, LDOs, and DDR regulators to keep the FPGA well-supplied. The company’s UCD90120A power-sequence controller is controllable and configurable using a 2-wire I2C bus.

Texas Instruments provides the schematic as well as test data for this reference design. In addition, design engineers can download the design files, or obtain the TSW14J56EVM board (Figure 2) as a fast way to test and evaluate this technology.

Figure 2: A ready-made version of Altera’s Arria V GZ FPGA Discrete Power Solution Reference Design is available to speed up test and development. All design files are free, so design engineers can modify their designs to meet specific needs. (Source: Texas Instruments)

Figure 2: A ready-made version of Altera’s Arria V GZ FPGA Discrete Power Solution Reference Design is available to speed up test and development. All design files are free, so design engineers can modify their designs to meet specific needs. (Source: Texas Instruments)

Over time, the quest to create smarter power systems has evolved. The ability of an embedded micro inside a programmable logic device to externally control its own power is one of the tools in a design engineer’s arsenal that can be used to optimize designs.

SN74AVC4T245

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

TPS7A4700

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

TPS7A7300

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

TPS51200

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

TPS54620

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

TPS76933

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

UCD90120A

For more information about this product, click here.

To request a sample, click here.  To buy now at Mouser, click here.

To buy now at Mouser, click here.

Author: Jon Gabay, Hearst Business Media

Advertisement

Learn more about Texas Instruments