The Atera SoC Developers Forum took place in Santa Clara a few days ago. The three technical presentations I attended were very well done and very well attended.

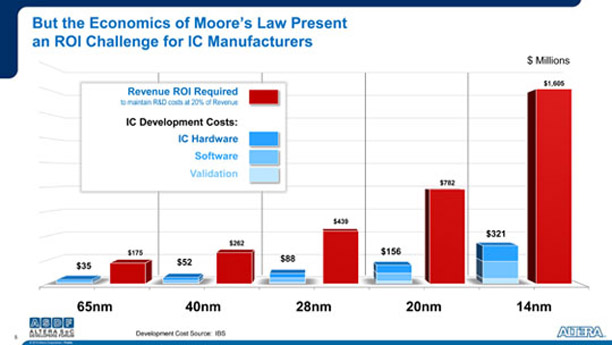

Altera’s Bradley Howe, Senior Vice President of Research and Development, gave a very interesting keynote. Brad said that while Moore’s law is alive and well and performance, die size, and power continue to fall, the cost of the latest node makes it out of reach for most projects. The chart in figure 1 shows that for the 14 nm node the sales revenue required to support development soars to over $1.5 B. Not a whole lot of products can reach this target.

Fig. 1: The harsh reality of advanced IC designs.

And now, he said, Altera is stepping up with SoC FPGAs like the Stratix 10, giving the next step in heterogeneous computing. Heterogeneous because the chip has multiple processing cores, multiple DSP cores and FPGA logic for accelerating any functions.

The Stratix 10 is certainly a leap forward. Altera says the device takes up to 70% lower power than prior-generation high-end FPGAs and SoCs. The chip has quad 64-bit Cortex-A53s combined with 10 Tflops of DSP performance and up to 5,510,000 1 GHz FPGA logic elements, plus 1,867,680 adaptive logic elements. The family uses Intel 14 nm Tri-Gate multi-die technology and have up to 72 high-speed (up to 30 Gbits/s) full-duplex transceivers.

The latest FPGAs also feature a HyperFlex architecture which has additional bypassable registers everywhere throughout the FPGA fabric. These additional Hyper-Registers are available on every interconnect routing segment and at the inputs of all functional blocks. They enable three key design techniques to achieve the 2x core performance increase:

Fine grained Hyper-Retiming to eliminate critical paths

Zero latency Hyper-Pipelining to eliminate routing delays

Flexible Hyper-Optimization to achieve best-in-class performance

Another new feature is the Secure Device Manager (SDM) available in all densities and device family variants. Serving as the central command center for the entire device, the it controls key operations such as configuration, device security, single event upset (SEU) responses, and power management.

Smaller, lower cost SoC devices can be found in Altera’s Aria and Cyclone product lines.

Advertisement

Learn more about Altera