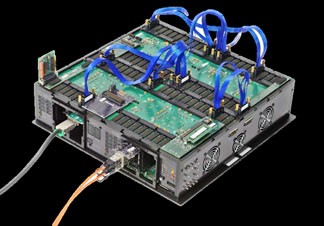

The HAPS-80 FPGA-based SoC/ASIC prototyping system offers a balance of simulation and emulation for reduced design time and supports up to 1.6 billion ASIC gates based on the Xilinx Virtex UltraScale FPGA. Its ProtoCompiler software automates partitioning and is said to reduce time to first prototype to less than two weeks, on average.

The system delivers up to 300 MHz for single FPGA designs, up to 100 MHz for multi-FPGA without pin-multiplexing, and up to 30 MHz for multi-FPGA with new proprietary high-speed pin-multiplexing. It uses new proprietary high-speed time-domain multiplexing (HSTDM) technology and features deep trace debug capabilities that are automatically inserted for greater efficiency and visibility, enabling the capture of thousands of RTL signals.

Advertisement

Learn more about Synopsys