Finding a problem with your prototype board is bad enough, but when the bug is in your latest IC masterpiece, you know it’s going to be a bad day. Heads may roll.

The verification of digital IC designs is a whole profession unto itself, and Mentor’s Tessent DefectSim works to bring similar thoroughness — not just to analog/AMS designs, but also to parts of your digital circuitry that aren’t covered by scan testing.

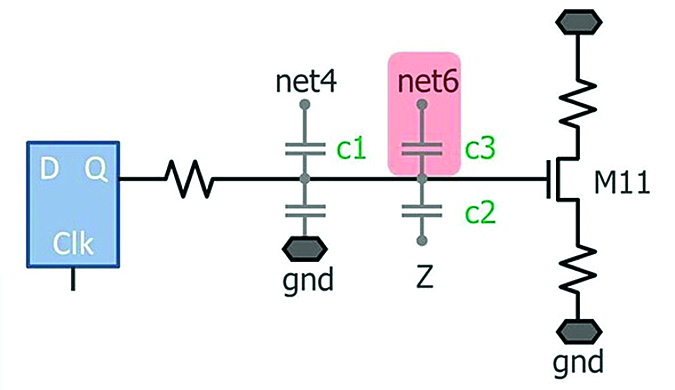

DefectSim uses the circuit’s schematic and layout to help it generate simulated defects, like shorts, opens, and process variations. The likelihood of each defect is calculated, guiding users in DFT and ATE efforts. SPICE simulation time is greatly reduced compared to simulating every potential defect. The test time for digital circuit blocks in ICs has greatly decreased in the last 20 years, thanks to scan-based design-for-test (DFT), automatic test pattern generation (ATPG) tools, and scan compression. These technologies have greatly reduced the number of test vectors applied by automatic test equipment (ATE) while maximizing the coverage of a wide range of defect types. But for analog circuits, test time has hardly decreased at all. DefectSim provides a measure of test quality and pathways to improve it while reducing test time, and it can facilitate compliance with high-rel requirements like ISO 26262.

The test time for digital circuit blocks in ICs has greatly decreased in the last 20 years, thanks to scan-based design-for-test (DFT), automatic test pattern generation (ATPG) tools, and scan compression. These technologies have greatly reduced the number of test vectors applied by automatic test equipment (ATE) while maximizing the coverage of a wide range of defect types. But for analog circuits, test time has hardly decreased at all. DefectSim provides a measure of test quality and pathways to improve it while reducing test time, and it can facilitate compliance with high-rel requirements like ISO 26262.

Advertisement

Learn more about Mentor Graphics