By Gina Roos, editor-in-chief

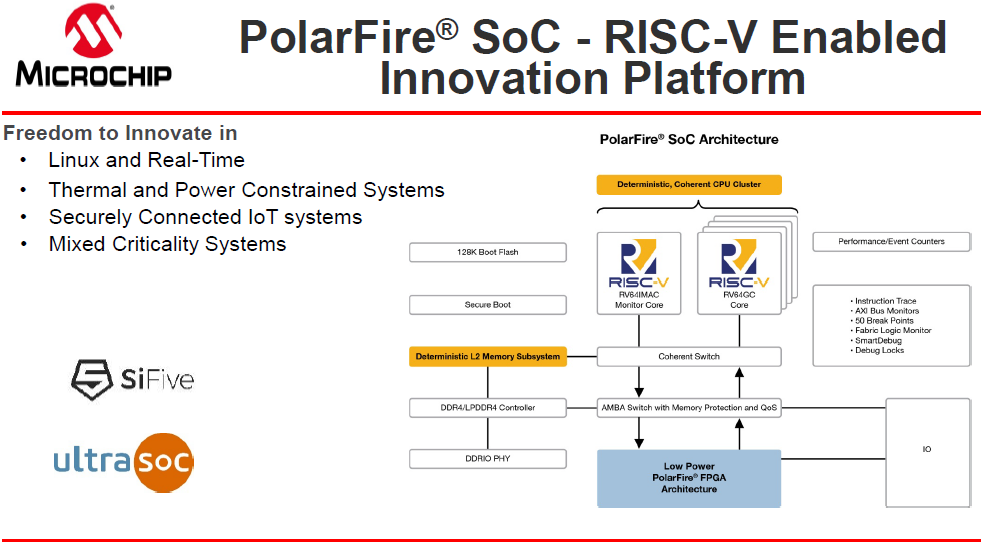

Delivering defense-grade security to embedded systems at the edge, Microchip Technology Inc. offers an early access program (EAP) for the PolarFire SoC FPGA. This platform is the first hardened real-time, Linux-capable, RISC-V–based microprocessor subsystem on the mid-range PolarFire FPGA family. This platform can be used in communications, defense, medical, and industrial automation applications.

The chip is the industry’s first SoC FPGA with a deterministic, coherent RISC-V CPU cluster and a deterministic L2 memory subsystem, enabling Linux plus real-time applications. The 2-MB memory subsystem can be configured as a cache, scratchpad, or a direct access memory. This means that embedded developers get the benefits of Linux in a deterministic architecture in combination with the security and low-power features of the PolarFire FPGA.

In addition, the PolarFire SoC architecture includes reliability and security features such as single error correction and double error detection (SEC-DED) on all memories, physical memory protection, a differential power analysis (DPA)-resistant crypto core, defense-grade secure boot, and 128 Kb of flash boot memory.

A key need solved by RISC-V was this concept of one processor that could run Linux and meet real-time requirements, said Ted Speers, technical fellow and head of product architecture and planning for Microchip’s FPGA business unit. “We already had low power and reliability in the bag with the PolarFire technology, but to really hit this out of the park, we needed the real-time processor. We wanted one processor to meet the needs of both [running Linux and real-time applications side by side] simultaneously.”

Designing with an FPGA and CPU on a single chip has continued to grow over the past several years, thanks to several key benefits for embedded designers. It improves the processing of specific tasks and enables customization and flexibility while reducing component count, power consumption, and board space.

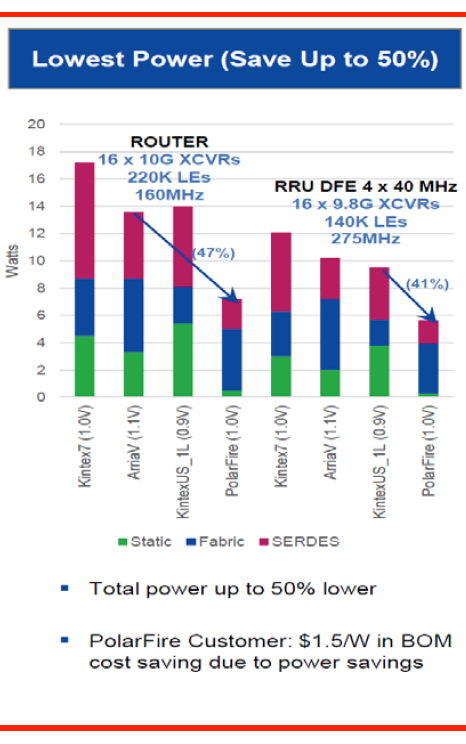

The deterministic and safety-critical PolarFire SoC delivers power efficiency that provides up to 50% lower power than competitive devices in the industry. As a result, it reduces the bill of materials by eliminating the need for fans and heat sinks.

“Our PolarFire technology offers 50% lower power in many cases than competing FPGAs,” said Speers. They can be used in small-form-factor environments where removing heat is a huge problem, enabling customers to remove the fans from the system, which saves cost and solves a lot of system constraints that are very difficult to design with, he added.

Getting customers to switch just because you offer lower power was tough, but in these applications, the PolarFire technology allows them to switch immediately because of the additional benefits, said Speers.

When the CPU and FPGA are on a single chip, there is a reduction in board space but also improved processing for specific tasks and less latency because it’s all on one die instead of going chip to chip on a board, said Speers. “With the programmable fabric, it also offers you a lot of customization and flexibility that you normally wouldn’t have. This is particularly important for emerging technologies where standards aren’t quite settled yet and you might need to make some changes in the field.

“The deterministic subsystem is where all the magic happens,” said Speers. “Microchip architected a chip that could run the mainstream Linux OS and all of its applications side by side with a real-time core within a deterministic and coherent memory subsystem.” And by moving from 1-MB to 2-MB L2 cache, customers can use 1 MB as local memory for deterministic real-time application by any of the four application cores.

As an added benefit, existing customers of Microchip’s SmartFusion 2 — the industry’s first SoC FPGA architecture with a full processor subsystem — can easily migrate to PolarFire SoC. PolarFire SoC’s 2-MB L2 memory subsystem can be configured as a local memory, and both platforms use common peripherals with firmware drivers and the same development tools.

Applications include thermally challenged environments such as industrial IoT switches and remote radio heads; battery-operated environments such as portable thermal imagers, portable ultrasound devices, secure military radios, and portable test and measure; and machine-learning and root-of-trust applications such as weapons platforms, secure military radios, and UAVs.

The chip is part of Microchip’s growing support for RISC-V design. Mi-V partners include WindRiver, Mentor Graphics, WolfSSL, ExpressLogic, Veridify, Hex-Five, and FreeRTOS as well as development tools from IAR systems and AdaCore.

As part of the EAP, qualified customers can start designing now with Microchip’s Libero SoC 12.3 FPGA design suite and SoftConsole 6.2 integrated development environment. They can also debug their embedded applications using Renode, a virtual model of the microprocessor subsystem.

Debug capabilities for the PolarFire SoC include instruction trace and passive run-time configurable Advanced eXtensible Interface (AXI) bus monitors from Mi-V partner UltraSoC, 50 breakpoints, FPGA fabric monitors, and Microchip’s built-in two-channel logic analyzer SmartDebug.

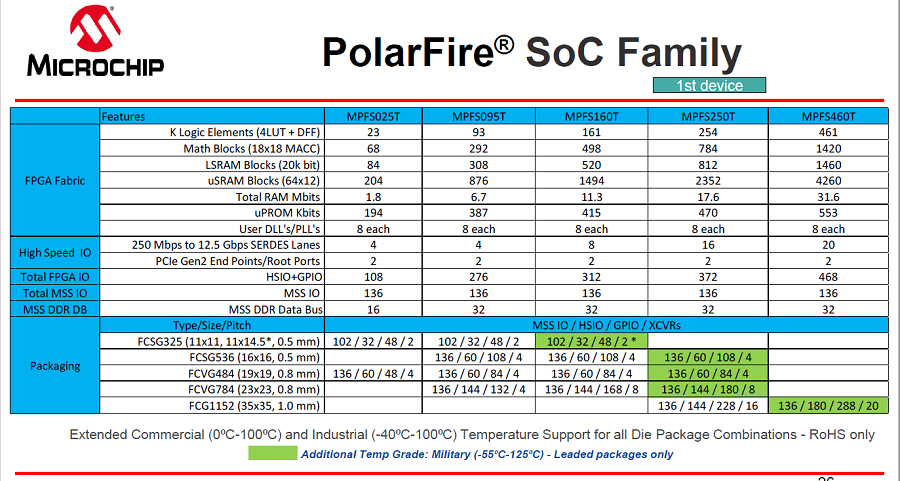

To qualify for the EAP, customers can contact . Customers can start designs now with access to the schematic and Gerber files for the PolarFire Icicle Kit that will be available in Q3 2020, as well as board design guidelines. The MPFS250T will start sampling in Q3 2020.

Advertisement

Learn more about Electronic Products Magazine