As the world becomes more interconnected and digital, software-defined radios (SDRs) become an essential part of our daily lives, with applications ranging from satellite communications and radar systems to mobile networks and medical imaging equipment. The technological requirements of wireless devices vary greatly in terms of compute capabilities, sample rates, tuning ranges, and size, weight, and power (SWaP); thus, commercial off-the-shelf (COTS) SDRs are designed with a wide range of features, greatly facilitated by their flexibility, modularity, and software-based nature.

Some characteristics and modules are common to all SDRs. Understanding component specification and how these parts work together is essential for SDR selection and design.

In this article, we discuss the general SDR architecture from a board-level perspective, covering how each element of an SDR is designed, developed, and implemented to satisfy high-performance requirements. We will present an overview of the basic aspects of an SDR, including the radio front end (RFE), the time component, the power distribution, and the digital element (typically based on FPGAs).

In high-performance SDRs, these different elements/components of the design are typically on separate printed-circuit boards (PCBs) in order to provide the best performance and minimize interference. Furthermore, we will discuss the basic concepts of the embedded engineering required to understand and properly design the complete SDR system.

Recommended

SDRs for IIoT, RF data, and manufacturing control

Basic concepts of the SDR

SDRs are RF transceivers that perform most of the radio functions and all of the signal processing in the software domain. This is achieved by using embedded digital components that are software-controlled as opposed to traditional RF hardware that is defined in hardware and, therefore, cannot be changed without a physical replacement. SDRs also provide a connection to external equipment, such as host computer systems, for further processing, storage, and monitoring functionalities.

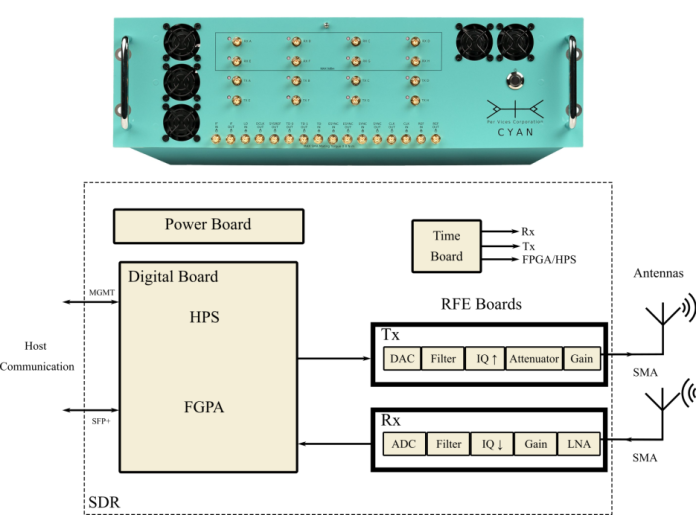

Although there are several different architectures available for SDRs, the highest-performance devices are usually composed of five PCBs: the transmit (Tx) and receive (Rx) RFE boards, the digital board, the timing board, and the power management board (see Figure 1).

The use of SDRs in various applications stems from their design flexibility and their performance capabilities, including high bandwidth, wide tuning range, multiple-input multiple-output (MIMO) operation, on-board computation power for parallel digital-signal–processing (DSP) functions, and the ability to pass data at very high rates to external equipment. COTS SDRs are typically compatible with open-source development and signal-processing toolkits, including GNU Radio, GNU Octave, and custom software based on C/C++ and Python.

Figure 1: External layout and interfaces, components, and internal boards of a high-end SDR (Source: Per Vices)

The RFE module consists of two basic boards: the transmitter and the receiver. The RFE is responsible for all of the essential analog functions of the SDR, including mixing, signal amplification, filtering, and antenna coupling, and typically covers everything from the RF input/output to the analog-to-digital converter/digital-to-analog converter (ADC/DAC).

One of the most important aspects of the RFE is the tuning range, which defines at what frequencies the SDR can operate within. The ranges can vary significantly but traditionally can be either from near DC to 6 GHz or near DC to 18 GHz for the higher-performance SDRs.

The other important aspect of the RFE is the bandwidth, which is the amount of the spectrum that can be captured at any given time on a single channel. The highest-performance SDRs in the market provide large instantaneous bandwidth of 1 GHz and 3 GHz, with multiple independent channels.

The receive and transmit portion of the SDR operate similarly, just in opposite directions. The Rx starts with an analog input and goes through the radio chain, which typically includes low-noise amplifiers (LNAs), variable attenuators, IQ down-converters, and anti-aliasing filters. It is then converted to a digital signal using an ADC and the digital data is passed to the FPGA, typically using a JESD interface.

The Tx functionality happens in reverse, starting at the signal being passed by the FPGA to the DAC, again using a JESD interface, and is then converted to the analog domain. Once in the analog domain, the signal propagates through several RF stages, including an anti-imaging filter, mixers, IQ up-converters, attenuators, and gain amplifiers, before reaching the antenna through an SMA, BNC, or N-type connector. Therefore, the SDR performance, in terms of sensitivity, tuning range, and MIMO capability, is greatly defined by the RFE design.

The digital board is the brain of the SDR and is a large part of what provides greater value to SDRs when compared with conventional RF systems. It performs all the DSP functions of the device, including modulation, demodulation, up-/down-converting, and waveform generations, while also providing means for a JESD interface and dedicated algorithms, such as communication protocols and artificial intelligence/machine learning (AI/ML).

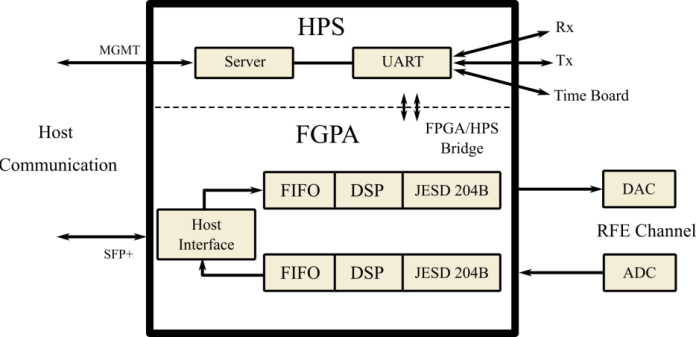

Computing power is an essential aspect of the digital board, and FPGA-based solutions are the best for parallel processing and low latency. These digital boards also provide data packetization over Ethernet optical links, which contain VITA49 IQ data in the Ethernet stack, with the highest-performing SDRs providing backhaul throughput of 4 × 40/100 Gbits/s over qSFP+. This method also allows direct connection between the FPGA and the 40/100-Gbits/s interface, which is fundamental to ensuring high data throughput between the SDR and the host system. The MGMT communications are handled by the hard-processor system (HPS) and allow for out-of-band control and management of the SDR, so it does not impact the data being captured or transmitted (see Figure 2).

Figure 2: Digital board architecture showing how the host interfaces with the FPGA, RFE, and other components (Source: Per Vices)

As is true for any electronic device, power distribution is an important element but becomes even more important for radio equipment to ensure the way power is routed does not cause electromagnetic interference (EMI). In SDRs, this is traditionally managed by a power board. The power board is responsible for delivering power to all the other boards of the SDR at the appropriate voltages, allowing proper functioning of each module without wasting unnecessary energy.

For instance, the oven-controlled oscillators (OCXOs) require a large amount of power to heat the electronic oven that maintains the crystal at a constant current, improving the frequency stability in about 100×. The thermal energy to heat the oven is generated using large amounts of electrical current, which must be handled by the power management system.

The optical transceivers are another component of the SDR that requires a significant amount of power. This is necessary to drive the 40/100 GBASE-R links.

At the RFE side, the power amplifiers that drive the antennas and the high-speed DAC/ADCs can be hungry energy consumers as well. In power-critical systems, the power board must be compatible with several power mode options, such as idle and sleep modes, that are often controlled by the HPS or the host system. Finally, the power board must provide energy to the thermal management fans, essential to avoid component damage due to overheating.

A crucial part of the SDR that is often overlooked is the timing board. It is the timing board that dictates the frequency and synchronicity accuracy of the device, often defining the performance limitation in terms of phase stability, phase coherency, drift, and data accuracy. The timing board is responsible for providing stable and precise clock signals to the digital board and the RFE boards, which are then used for waveform generation, signal tuning, communication clocking, ADC/DAC sampling rates, time counting, and channel synchronicity.

High-end SDRs use a main 10-MHz signal as the reference clock, often generated by a high-stability OCXO system. The 10-MHz signal then passes through PLLs, which implement clock multiplication, and clock recovery, all of which are essential for the RFE. The timing board also applies jitter cleaners (for optimization of jitter), clock dividers (for modules that require lower frequencies), and fanout buffers (for safe and clean clock distribution). Although high-performance SDRs provide on-board OCXO-based internal references, the use of external clocks may also be possible using some SDRs, enabling synchronicity with multiple SDRs or other equipment.

Design and development of SDRs

As mentioned earlier, the application range of SDRs covers a wide variety of use cases, with very different performance requirements and system limitations. Therefore, SDRs are often designed to favor flexibility and modularity, allowing users to decide which RF parameters must be optimized to satisfy their performance and SWaP requirements.

For instance, to select or design a transceiver for a phased-array system, you need to ensure that a large number of independent channels and the phase coherency between channels is highly accurate and stable, whereas a spectrum-monitoring application requires high instantaneous bandwidth and data throughput/backhaul to capture and store as much data as possible in a short amount of time.

Another example are SDRs designed for satellite ground communications, where these systems must be optimized for receiver sensitivity and tuning range due to the use of high frequencies (Ka bands) that are more prone to atmospheric attenuation. Network applications, especially low-latency communication architectures, require more focus on the computation capabilities of the SDR, and devices with FPGA-based digital units are preferred due to their parallel DSP capabilities, low-latency computation, and high throughput of data over optical links.

When designing a custom SDR or selecting an SDR for an application, several figures of merit and requirements must be considered to balance which performance parameters and features will be optimized and which ones will be treated as secondary or tertiary.

Tuning range, for instance, depends largely on the frequency required for the application: If only a few narrow frequencies are used, SDRs with limited tuning ranges can be used and usually decrease the SWaP and total cost, whereas more general-purpose applications that require wider tuning ranges are typically designed without SWaP in consideration. It is not to say that you cannot have both, but that will depend on the SDR, manufacturer, and costs.

Other RFE parameters include sensitivity and dynamic range, which defines the minimum and maximum detectable signals of the receiver and depends on path loss, noise level, and external interference. The number of channels is also important, depending on budget, system features, and MIMO capability. MIMO applications must also have excellent phase coherency between channels, which allows synchronicity. On the digital side, latency and computation power are major parameters that define how well the SDR can communicate and process signals at high speed.

Backhaul capability defines the maximum data throughput, which is greatly affected by the type of host interface, FPGA specifications, communication protocols, and RF bandwidth as well as the number of channels — the data captured needs to go somewhere if processing is not performed on the FPGA. All of these parameters must be weighed against the SWaP and cost requirements of the system, and it is the designer’s job to find the best combination and compromise between desired performance and physical/budget limitations.

Implementation

The implementation of the design aspects of the SDR depends mostly on the performance objective and the target application. If the application requires more sensitivity to improve signal-to-noise ratio (SNR) and better receive weak signals, one can select several design strategies: Implement high-quality LNAs, use in-phase and quadrature (IQ) mixing to suppress the side bands that contain noise or interference, remove the noise coming from the power supply using bypasses, and optimize the antenna impedance.

Each strategy has pros and cons that must be weighed against the other RFE requirements, limitations, and project budget. Another issue regarding the RF channels is phase coherency, which is essential to drive phased-array antennas. Phase coherency can be improved using high-quality phase-locked–loop (PLL) architectures to distribute the same local oscillator (LO) frequencies to all the independent signal chains.

Tuning range usually defines the application coverage of the SDR, as it limits the possible frequencies of the RFE. Tuning range can be largely increased by the implementation of several mixing stages, which requires the synthetization of high frequencies for the IQ mixers of the Tx and Rx channels (see Figure 3).

IQ mixers are robust mixing circuits that use both quadrature and in-phase signals to achieve side-band suppression and image rejection while also providing enough flexibility to enable large tuning ranges. The implementation of digital IQ mixers inside the FPGA can significantly improve reconfigurability over the RFE tuning; e.g., numerically controlled oscillator (NCO) CORDIC mixers can be designed directly in the FPGA for up-/down-conversion and easily modified via software.

Figure 3: IQ mixer showing the transmission between the transmitter and receiver sides (Source: Per Vices)

Latency is one of the most important aspects of any communication system, so it is expected that it plays a major role in SDR design. The total latency of an SDR is a result of a combination of factors, including DAC/ADC delay, the interface to the FPGA (JESD204), on-board DSP operations (including modulation, demodulation, channelization, and filtering), and the communication with the host system or external equipment. The implementation of low-latency modems requires high-performance FPGAs, which allow the designer to implement custom first-in/first-out (FIFO) buffers and pipelines that can improve the signal flow and reduce the time period for each operation.

High data throughput is important in network solutions, especially considering the 5G era. The first method to improve this feature is to implement IP cores in the FPGA that are capable of packetizing data for different types of Ethernet protocols. It is important to also keep in mind that the data-transferring process must be highly deterministic to avoid information lost and corruption. For that, the system requires sophisticated clocking and time synchronization, which prevents underflowing and overflowing of the packet buffer by ensuring that the transmission process starts at the proper time.

Furthermore, meeting timing requirements becomes a real challenge when working with high-throughput SDRs and implementing an FPGA-based system that supports data transmission rates of 100G, which addresses a variety of limitations but comes with its own design challenges and requires strict adherence to good design practices.

Some of these practices include correct handling of signals and reducing combinatorial paths. This is important, as each input signal needs to be stable before and after the rising edge of the clock in order for the sequential combinatorial logic to be executed in each signal path while respecting the clock signal.

Conclusion

Due to their flexibility and wide application range, COTS SDRs are designed for a variety of performance requirements, feature capabilities, and SWaP configurations. Each SDR is different, and selecting and customizing an SDR for the specific application is the best way to reduce development cost and time.

For SDRs that are modular in nature, as those described in this article, each board functionality can be customized to comply with a certain application, allowing the designer to address several RF requirements through minor modifications to just one element of the SDR as opposed to starting from scratch. Proper SDR customization is crucial to optimize both performance and cost of modern radio systems and should not be overlooked by RF designers or system integrators.

About the author

Brendon McHugh is a field application engineer and technical writer at Per Vices. He has a degree in theoretical physics from the University of Toronto. Per Vices has extensive experience in designing, developing, building, and integrating SDRs for various applications, including but not limited to test & measurement, radar, GNSS, spectrum monitoring, communications, and aerospace/defense. Visit pervices.com or contact solutions@pervices.com for more information.

Brendon McHugh is a field application engineer and technical writer at Per Vices. He has a degree in theoretical physics from the University of Toronto. Per Vices has extensive experience in designing, developing, building, and integrating SDRs for various applications, including but not limited to test & measurement, radar, GNSS, spectrum monitoring, communications, and aerospace/defense. Visit pervices.com or contact solutions@pervices.com for more information.

Advertisement